# ขั้นตอนวิธีพันธุกรรมสำหรับวงจรเชิงวิวัฒนาการแบบขนาน

นายยุทธนา เจวจินดา

วิทยานิพนธ์นี้เป็นส่วนหนึ่งของการศึกษาตามหลักสูตรปริญญาวิศวกรรมศาสตรดุษฎีบัณฑิต สาขาวิชาวิศวกรรมคอมพิวเตอร์ ภาควิชาวิศวกรรมคอมพิวเตอร์ คณะวิศวกรรมศาสตร์ จุฬาลงกรณ์มหาวิทยาลัย ปีการศึกษา 2551 ลิขสิทธิ์ของจุฬาลงกรณ์มหาวิทยาลัย

# PARALLEL APPROACH TO GENETIC ALGORITHMS FOR EVOLVABLE HARDWARE

Mr. Yutana Jewajinda

A Dissertation Submitted in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy Program in Computer Engineering

Department of Computer Engineering

Faculty of Engineering

Chulalongkorn University

Academic Year 2008

Copyright of Chulalongkorn University

| Thesis Title     | Parallel Approach to Genetic Algorithms for Evolvable                                       |

|------------------|---------------------------------------------------------------------------------------------|

|                  | Hardware                                                                                    |

| Ву               | Yutana Jewajinda                                                                            |

| Field of Study   | Computer Engineering                                                                        |

| Advisor          | Professor Prabhas Chongstitvatana, Ph.D.                                                    |

|                  | e Faculty of Engineering, Chulalongkorn University in Partial ments for the Doctoral Degree |

| *******          | Dean of the Faculty of Engineering                                                          |

| (Associ          | ate Professor Boonsom Lerdhirunwong, Dr.Ing.)                                               |

| THESIS COMMITTEE |                                                                                             |

|                  | 9018 Chairman                                                                               |

| (Associ          | ate Professor Sartid Vongpradhip, Ph.D.)                                                    |

| 9.               | Eliptitotan Advisor                                                                         |

| (Profes          | sor Prabhas Chongstitvatana, Ph.D.)                                                         |

|                  | Nau Examiner                                                                                |

| (Assoc           | iate Professor Somchai Prasitjutrakul, Ph.D.)                                               |

|                  | Davida Sutivong Examiner                                                                    |

|                  | ant Professor Daricha Sutivong, Ph.D.)  Hown Christian External Examiner                    |

| (Assoc           | iate Professor Kosin Chamnongthai, Ph.D.)                                                   |

ยุทธนา เจวจินดา : ขั้นตอนวิธีพันธุกรรมสำหรับวงจรเชิงวิวัฒนาการแบบขนาน (PARALLEL APPROACH TO GENETIC ALGORITHMS FOR EVOLVABLE HARDWARE). อ.ที่ปรึกษาวิทยานิพนธ์หลัก : ศ. ดร.ประภาส จงสถิตย์วัฒนา, 111 หน้า

วิทยานิพนธ์นี้นำเสนอขั้นตอนวิธีพันธุกรรมอย่างย่อแบบเชล ซึ่งเป็นขั้นตอนวิธี พันธุกรรมแบบขนานสำหรับประยุกต์ใช้งานกับวงจรเชิงวิวัฒนาการ ขั้นตอนวิธีพันธุกรรมอย่าง ย่อแบบเชล ใช้การแลกเปลี่ยนโมเดลความน่าจะเป็นของกลุ่มประชากรแทนการแลกเปลี่ยน ประชากรโดยตรง อีกทั้งใช้หลักการเก็บประชากรที่ดีที่สุด ขั้นตอนวิธีพันธุกรรมอย่างย่อแบบเชล ใช้หลักการปรับตัวในการรวมโมเดลความน่าจะเป็นของกลุ่มประชากรเข้าด้วยกัน และสามารถใช้ แก้ปัญหาขั้นยากที่มีกรอบจำกัดได้ ขั้นตอนวิธีพันธุกรรมอย่างย่อแบบเชลถูกออกแบบมา เหมาะสมสำหรับสร้างเป็นวงจรเชิงเลข มีการนำเสนอสถาปัตยกรรมฮาร์ดแวร์แบบปรับขยายได้ ของขั้นตอนวิธีพันธุกรรมอย่างย่อแบบเซล วิทยานิพนธ์ยังได้นำเสนอวงจรเชิงวิวัฒนาการซึ่งใช้ งานร่วมกันระหว่างวิธีพันธุกรรมอย่างย่อแบบเซลและโคร่งข่ายประสาทเทียมโดยใช้หลักการ สถาปัตยกรรมฮาร์ดแวร์แบบเป็นชั้น ได้ทำการประยุกต์วงจรเชิงวิวัฒนาการซึ่งใช้งานร่วมกัน ระหว่างวิธีพันธุกรรมอย่างย่อแบบเซลและโคร่งข่ายประสาทเทียมกับปัญหาการแยกสัญญาณ คลื่นไฟฟ้าหัวใจ ซึ่งแสดงให้เป็นว่าวิธีพันธุกรรมอย่างย่อแบบเซลและวงจรเชิงวิวัฒนาการที่ นำเสนอ สามารถนำไปแก้ปัญหาจริงได้

| ภาควิชา วิศวกรรมคอมพิวเตอร์ | ลายมือชื่อนิสิต                       |

|-----------------------------|---------------------------------------|

|                             | ลายมือชื่อ อ.ที่ปรึกษาวิทยานิพนธ์หลัก |

| ปีการศึกษา 2551             |                                       |

: MAJOR COMPUTER ENGINEERING # # 4771820721

EVOLVABLE HARDWARE / GENETIC ALGORITHM / KEYWORDS: PARALLEL GENETIC ALGORITHM

YUTANA JEWAJINDA : PARALLEL APPROACH TO GENETIC ALGORITHMS FOR EVOLVABLE HARDWARE. ADVISOR: PROF. PRABHAS CHONGSTITVATANA, Ph.D., 111 pp.

The thesis proposes the cellular compact genetic algorithm (CCGA), which is a parallel probabilistic model-building genetic algorithm for evolvable hardware. CCGA replaces traditional migration of individuals with the probabilistic migration. Each CCGA node uses the traditional compact GA with elitism. CCGA employs adaptive combination of probability vectors from its neighbors. CCGA can solve hard problems of bounded difficulty. With parallel approach, CCGA supports scalability. In addition, CCGA is designed for hardware implementation. The scalable hardware architecture for CCGA is proposed. For each node of CCGA, the scalable hardware architecture supports expandable number of variables to be optimized with flexible precision and expandable chromosome length. Evolvable hardware based-on Cellular Genetic Algorithm (CCGA) and Block-based neural network (BBNN) is presented. The layer-based architecture is proposed for integrating CCGA with BBNN in hardware. A hardware design of BBNN neurons is proposed. The link-multiplexed concept is used for hardware design of BBNN neurons. The proposed evolvable hardware based-on CCGA and BBNN is applied to the problem of online ECG signal classification. This demonstrates that CCGA can solve the real-world problems. The proposed evolvable hardware can be implemented in FPGA or ASIC for a portable personalized ECG signal classifications for long term patient monitoring.

Department: Computer Engineering Field of Study: Computer Engineering

Student's Signature Tesz, i. d. S Advisor's Signature O-Chyptitahu

Academic Year: 2008

# Acknowledgement

There are many people to whom I am grateful for helping to get all the way to finish up my dissertation. Foremost, I am thankful to the Lord for inspiring me to rethink about beginning my Ph.D. study once again in Thailand after long years of discouraging back here in the land of smiles.

I wouldn't be this far for my Ph.D. study at Chula if it wasn't my thesis advisor, Professor Prabhas Chongstitvatana, who gave me this great opportunity of working with him and other members of the Prof. Prabhas's lab. Prof. Prabhas is a great teacher and a bottomless source of inspiration when I felt like I wanted to give up many times.

Finally, I would like to say "Thank you" to my mother for her supporting.

# Contents

| Abstract (Thai)                                                     |   |

|---------------------------------------------------------------------|---|

| Abstract (English)                                                  |   |

| Acknowledgement                                                     |   |

| Contents                                                            |   |

| List of Tables                                                      |   |

| List of Figures                                                     |   |

| Chapter                                                             |   |

| I Introduction                                                      |   |

| 1.1 Evolvable Hardware                                              |   |

| 1.1.1 Evolvable Hardware: Basic Concepts                            |   |

| 1.1.2 Application of EHW                                            |   |

| 1.2 From Genetic Algorithms to Probabilistic Model-Building GAs     |   |

| 1.2.1 Genetic Algorithms                                            |   |

| 1.2.2 Probabilistic Model-Building Genetic Algorithms: concept      |   |

| 1.2.3 Parallel Genetic Algorithms                                   |   |

| 1.3 Thesis Objectives                                               |   |

| 1.4 Contributions                                                   |   |

| 1.5 Dissertation layout                                             |   |

| 1.6 Publications                                                    |   |

| II Literature Reviews                                               |   |

| 2.1 Evolvable hardware: vision and motivation                       |   |

| 2.1.1 Evolving connectionist system                                 |   |

| 2.1.2 Bio-inspired hardware model                                   |   |

| 2.1.3 Evolvable hardware based-on evolving connectionist system     | 1 |

| and bio-inspired machines                                           |   |

| 2.1.4 Dualism of evolvable hardware                                 |   |

| 2.1.5 Evolutionary artificial neural network and evolvable hardware |   |

| 2.2 Evolvable Hardware: survey                                      |   |

| 2.3 Probabilistic Model-Building Genetic Algorithms                 |   |

| Chapter                                                              | Page |

|----------------------------------------------------------------------|------|

| 2.3.1 Without dependency                                             | 19   |

| 2.3.2 Pairwise Dependency                                            | 23   |

| 2.3.3 Multivariate dependencies                                      | 24   |

| 2.4 Test Functions for genetic algorithms                            | 25   |

| 2.4.1 Problems involving lower order BBs                             | 25   |

| 2.4.2 Problems involving higher order BBs                            | 25   |

| 2.4.3 Continuous and multimodal functions                            | 26   |

| 2.5 Parallel EDA with probability model migration                    | 28   |

| 2.6 Hardware implementation of genetic algorithms                    | 29   |

| 2.6.1 Direct hardware implementation of the basic genetic algorithms | 30   |

| 2.6.2 Parallelized hardware implementation of the existing GAs       | 31   |

| 2.6.3 New genetic algorithms for hardware implementation             | 32   |

| 2.7 Block-based neural network                                       | 33   |

| 2.8 Hardware implementation of neural network: a survey              | 35   |

| 2.9 Online ECG signal classification                                 | 38   |

| III Cellular Compact Genetic Algorithms                              | 43   |

| 3.1 Cooperative compact genetic algorithm                            | 43   |

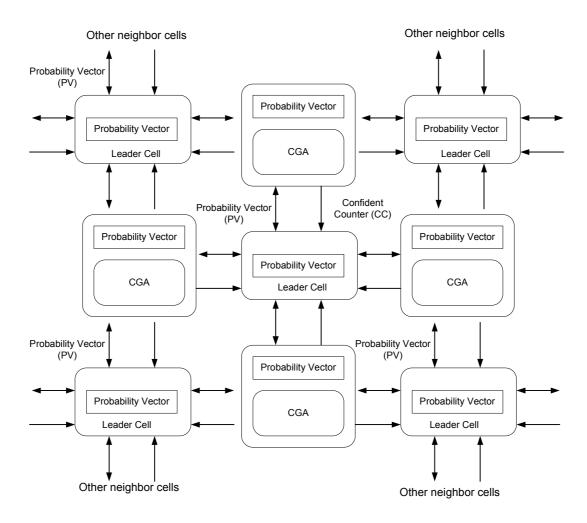

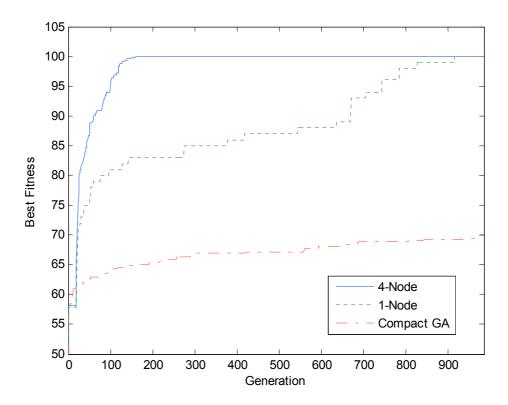

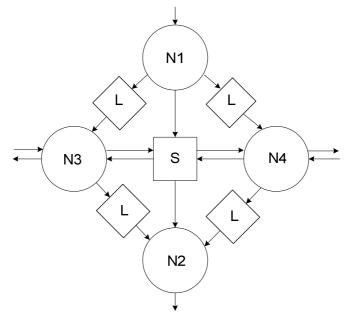

| 3.1.1 CoCGA Topology                                                 | 44   |

| 3.1.2 CoCGA Algorithm                                                | 44   |

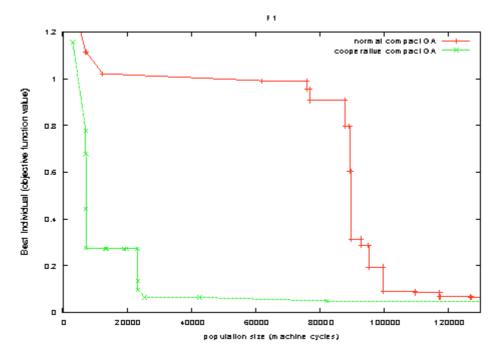

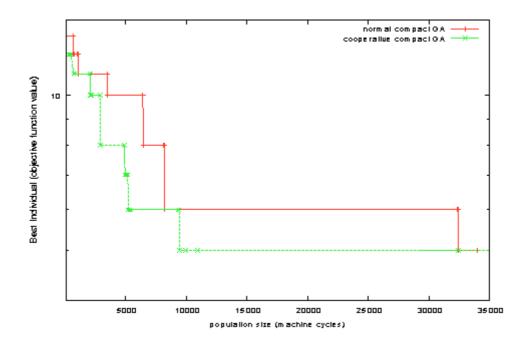

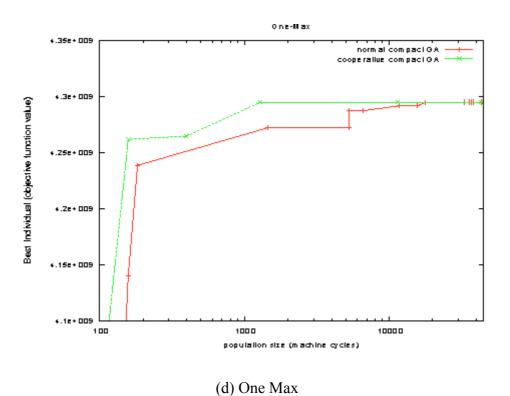

| 3.1.3 Benchmark problems and experimental results                    | 46   |

| 3.1.4 Hardware Architecture and Implementation of CoCGA              | 50   |

| 3.2 Cellular Compact Genetic Algorithm                               | 53   |

| 3.2.1 CCGA Topology                                                  | 53   |

| 3.2.2 CCGA Algorithm                                                 | 54   |

| 3.2.3 Benchmarks problems and experimental results                   | 53   |

| 3.2.4 Hardware Architecture and Implementation of CCGA               | 63   |

| 3.3 Discussion                                                       | 66   |

| 3.4 Summary                                                          | 67   |

| IV Evolvable hardware based-on CCGA and BBNN                         | 69   |

| 4.1 Hardware Architecture for BBNN                                   | 70   |

| Chapter                                                           | Page |

|-------------------------------------------------------------------|------|

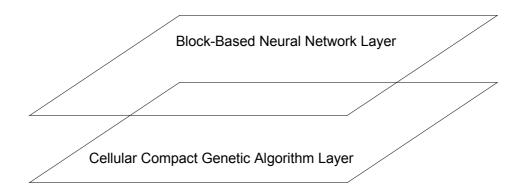

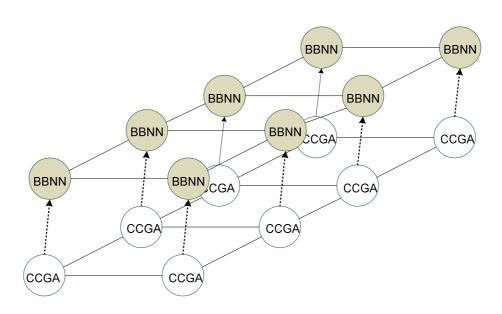

| 4.2 Layer-based Architecture for integration of CCGA and BBNN     | 71   |

| 4.3 FPGA Implementation                                           | 72   |

| 4.4 XOR problem                                                   | 74   |

| 4.5 Discussion                                                    | 76   |

| 4.6 Summary                                                       | 77   |

| V Evolvable Hardware for Automatic and ECG Signal Classification. | 79   |

| 5.1 ECG Data                                                      | 80   |

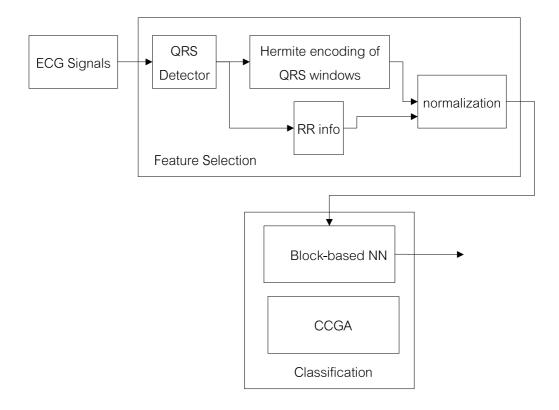

| 5.2 Feature selection                                             | 87   |

| 5.3 Classification process                                        | 90   |

| 5.4 Experimental Results                                          | 91   |

| 5.5 Discussion                                                    | 93   |

| 5.6 Summary                                                       | 94   |

| VI Conclusions                                                    | 96   |

| 6.1 What Has Been Done                                            | 96   |

| 6.2 Main Conclusions                                              | 97   |

| 6.3 Future Work                                                   | 98   |

| References                                                        | 99   |

| Biography                                                         | 111  |

# **List of Tables**

| Tab | le                                                                        | Page |

|-----|---------------------------------------------------------------------------|------|

| 2.1 | An example of $D_l^{Se}$                                                  | 21   |

| 3.1 | The performance comparison in term of number of clock cycles              | 50   |

| 3.2 | The performance comparison in term of FPGA hardware resources             | 53   |

| 3.3 | FPGA Hardware Resource Xilinx Virtex-5 LX50                               | 67   |

| 3.4 | Comparison of FPGA resources                                              | 68   |

| 4.1 | FPGA Hardware Resource Xilinx Virtex-5 LX50                               | 75   |

| 5.1 | Mapping the MIT-BIH arrhythmia database heartbeat types to the AMMI       |      |

|     | heartbeat classes                                                         | 81   |

| 5.2 | Heartbeat annotation codes in MIT-BIH arrhythmia database                 | 82   |

| 5.3 | Summary of the database and beat types (entire records)                   | 83   |

| 5.4 | Heartbeat types associated with the extracted beat for first five minutes |      |

|     | and first part of the training set                                        | 85   |

| 5.5 | Records in training and testing sets from the MIT-BIH arrhythmia          |      |

|     | database                                                                  | 86   |

| 5.6 | Summary of beat-by-beat classification results for the five classes       | 92   |

| 5.7 | Performance comparison of VEB and SVEB Detection (in percent)             | 93   |

# **List of Figures**

| Figure                                                                   | Page |

|--------------------------------------------------------------------------|------|

| 1.1 Overview of Evolvable Hardware                                       | 2    |

| 1.2 Genetic Algorithms as a mean for hardware evolution                  | 4    |

| 1.3 A typical EH device for control application                          | 5    |

| 1.4 A typical EH device for online classification                        | 5    |

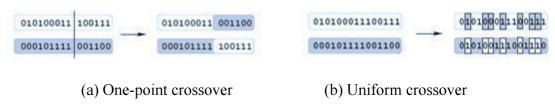

| 1.5 An illustrative example of two common two-parent crossover operators | 7    |

| 1.6 Pseudo-code of the general PMBGA procedure                           | 7    |

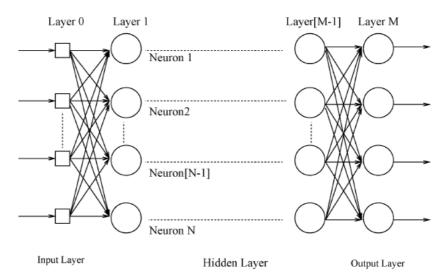

| 2.1: Feed forward Artificial Neural Network                              | 18   |

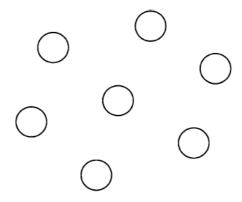

| 2.2 Graphical models with no interactions                                | 20   |

| 2.3 Pseudocode of UMDA                                                   | 20   |

| 2.4 Pseudocode of PBIL                                                   | 21   |

| 2.5 Pseudocode of compact GA                                             | 22   |

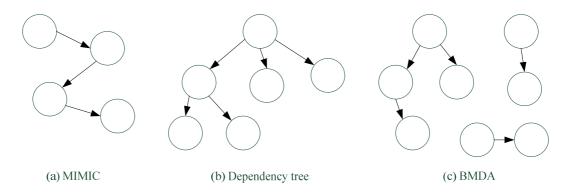

| 2.6 Graphical model of pairwire dependency algorithms                    | 23   |

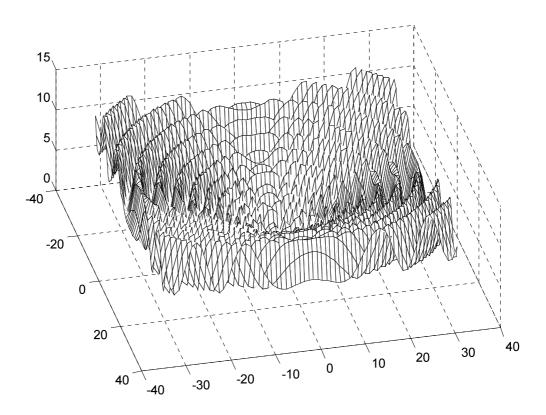

| 2.7 Plot of the circle function                                          | 27   |

| 2.8 Plot of the Schaffer's function with 2-D (n=2)                       | 28   |

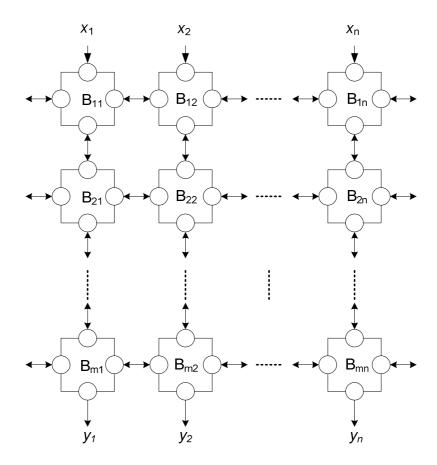

| 2.9 Structure of BBNNs                                                   | 34   |

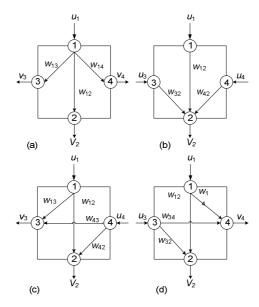

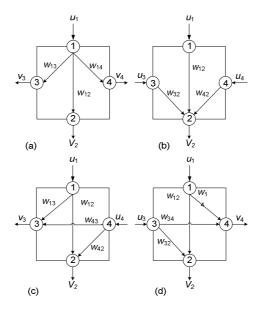

| 2.10 Four different internal configurations of a BBNN block              | 28   |

| 2.11 Structure of MLP                                                    | 36   |

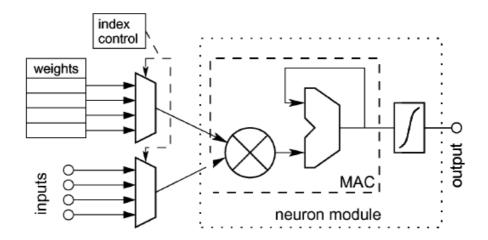

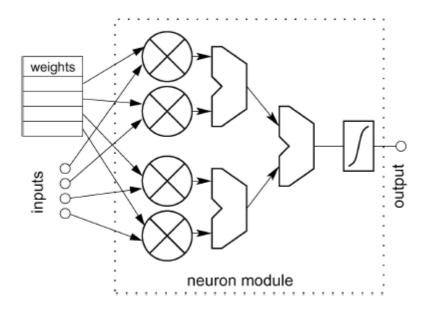

| 2.12 Shared multiply-accumulate (MAC) unit                               | 37   |

| 2.13 Parallel multiply-accumulate (MAC) unit                             | 37   |

| 2.14 Typical ECG waveform                                                | 39   |

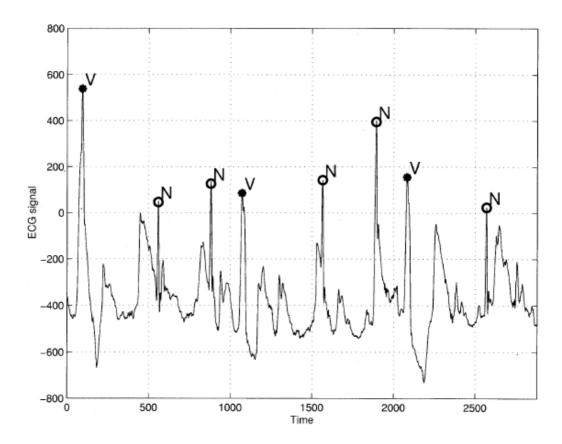

| 2.15 Examples of real ECG recording of two different rhythm types        | 40   |

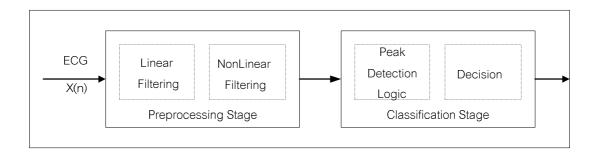

| 2.16 Common structure of the QRS detectors                               | 41   |

| 3.1 Topology of Cooperative Compact GAs                                  | 45   |

| 3.2 Pseudocode of CoCGA (left for leader cell, right for normal cell)    | 47   |

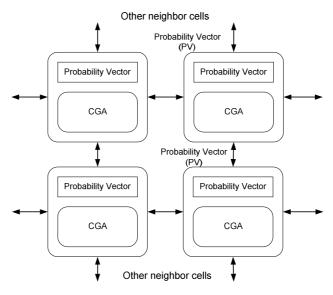

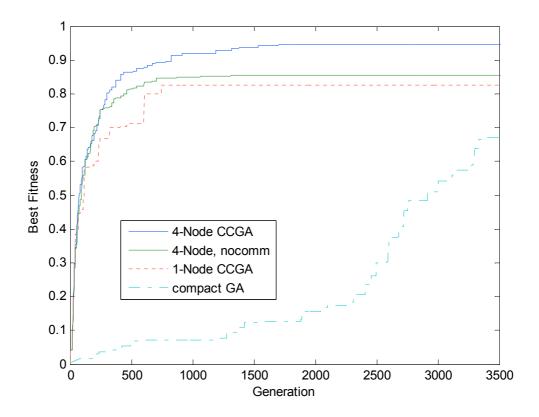

| 3.3 Comparison of CGA and CoCGA performance                              | 48   |

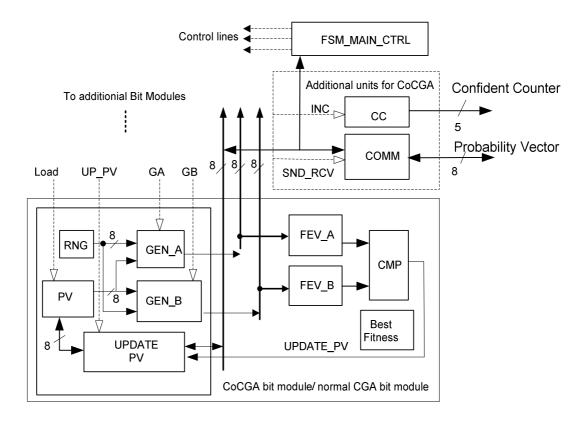

| 3.4 Hardware block diagram of a normal CoCGA cell                        | 52   |

| 3.5 Hardware design of two-neighbor cells                                | 52   |

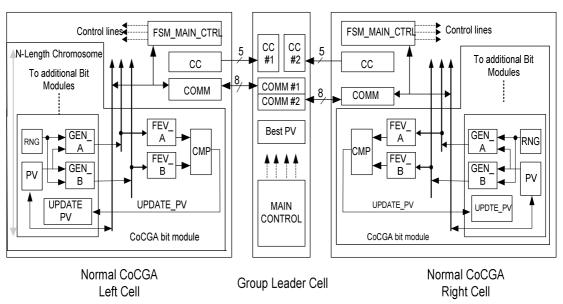

| 3.6 Topology of cellular compact GA                                      | 54   |

| Figu | ure                                                                       | Page |

|------|---------------------------------------------------------------------------|------|

| 3.7  | Modification of compact GA to realize persistent elitism                  | 55   |

| 3.8  | Modification of compact GA to realize non-persistent elitism              | 56   |

| 3.9  | Pseudocode of cellular compact GA                                         | 58   |

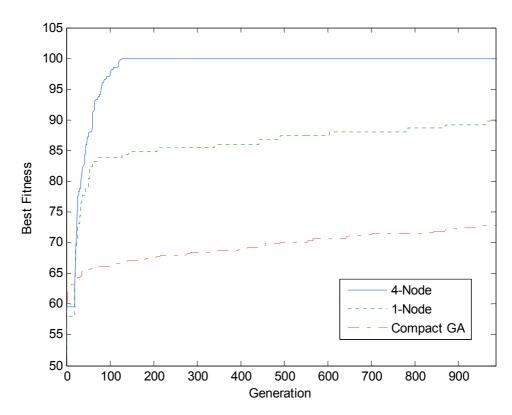

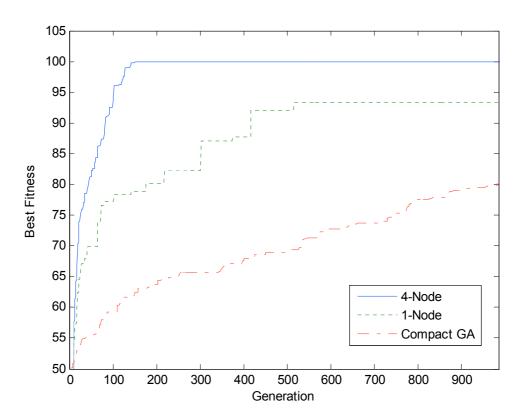

| 3.10 | Performance of the CCGA on OneMax                                         | 60   |

| 3.11 | Performance of the CCGA on MDP                                            | 61   |

| 3.12 | 2 Performance of the CCGA on 90-bit of the three-trap problem             | 61   |

| 3.13 | Performance of the CCGA on 120-bit of the four-trap problem               | 62   |

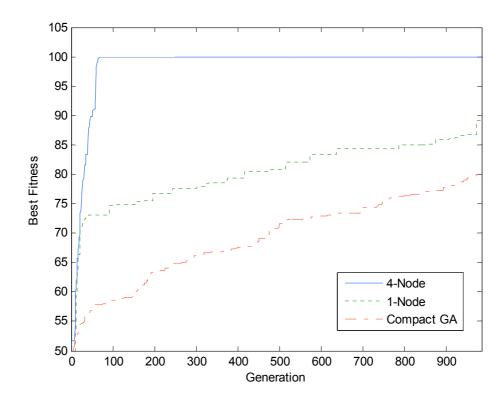

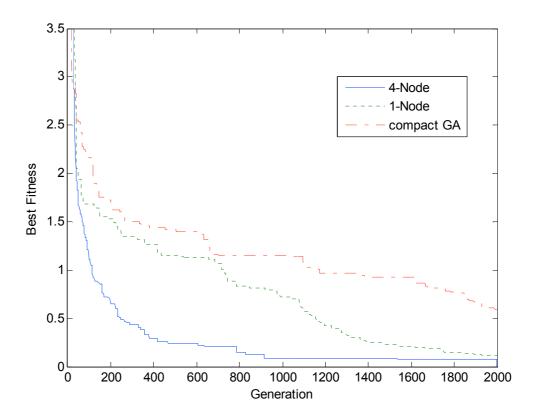

| 3.14 | 4 Performance of the CCGA on 30-bit of the circle function                | 62   |

| 3.15 | 5 Performance of the CCGA on 75-bit of the Schaffer function              | 63   |

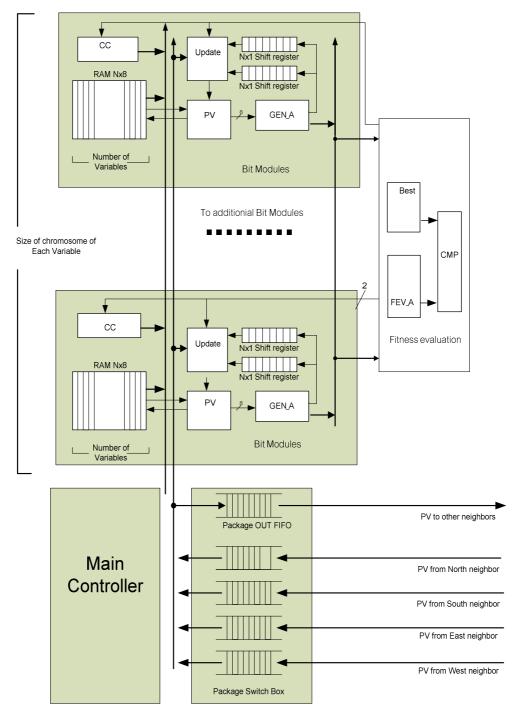

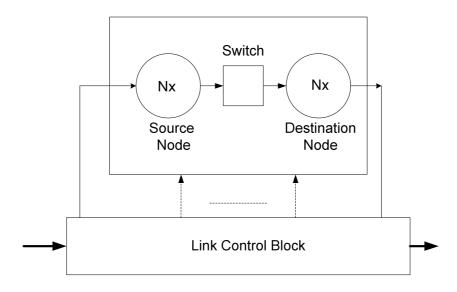

| 3.16 | The proposed hardware architecture for CCGA                               | 65   |

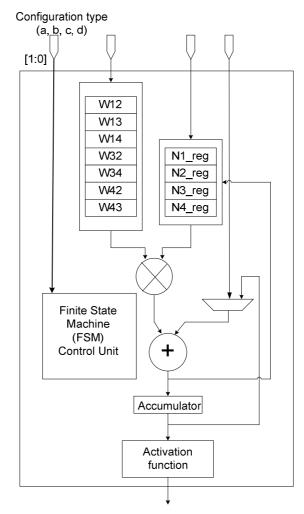

| 4.1  | A BBNN block                                                              | 71   |

| 4.2  | Link-multiplexed BBNN block                                               | 71   |

| 4.3  | Hardware design of general neuron three inputs and three outputs          | 73   |

| 4.4  | Layer-based architecture for evolvable hardware based-on BBNN and         |      |

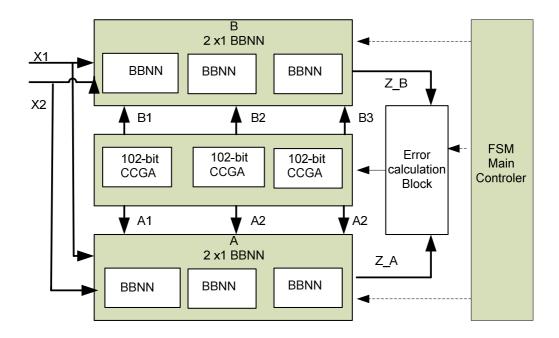

|      | CCGA                                                                      | 73   |

| 4.5  | 2 x 4 BBNN layer and CCGA                                                 | 74   |

| 4.6  | Block diagram of BBNN and CCGA for XOR                                    | 74   |

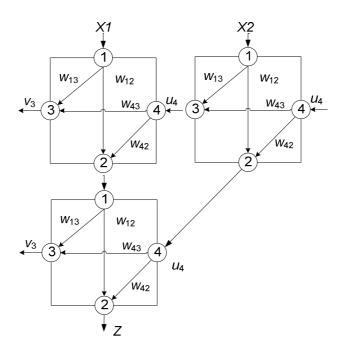

| 4.7  | A structure of XOR that has fitness value of 0.998                        | 77   |

| 4.8  | Fitness value in training process of XOR                                  | 78   |

| 5.1  | Our method of ECGs signal classification                                  | 79   |

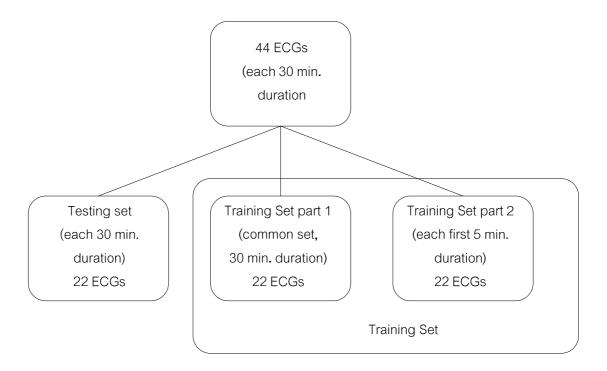

| 5.2  | Division of the arrhythmia database into training and testing sets        | 86   |

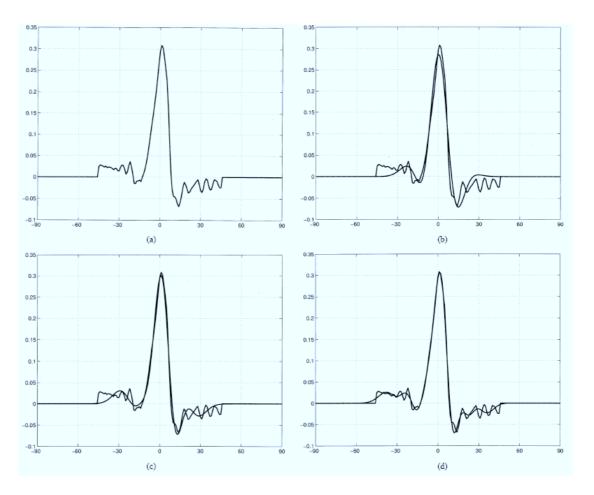

| 5.3  | Expanded QRS complex of (a) ECG waveform and its estimation using         |      |

|      | (b) 6, (c) 9, and (d) 15 Hermite basis functions                          | 80   |

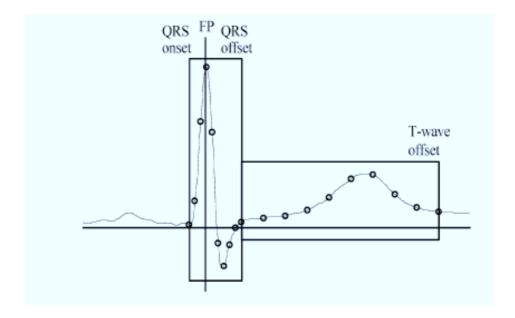

| 5.4  | Time-sampling methods for extracting ECG morphology features              | 80   |

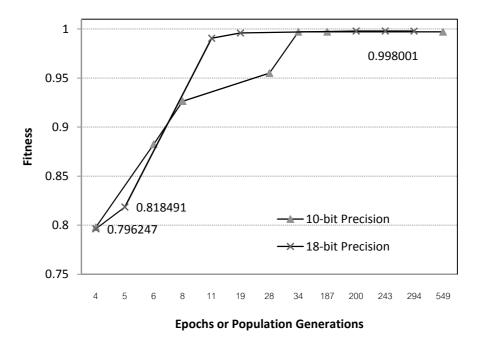

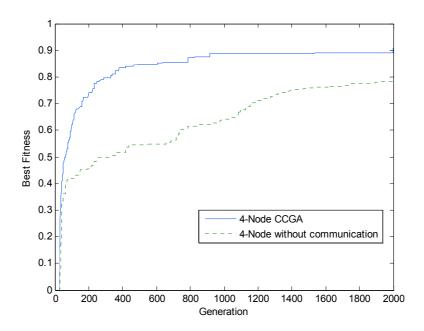

| 5.5  | Fitness and number of generation (function evaluation)                    | 91   |

| 5.6  | Fitness performance measures used for (a) distinguishing vebs from non-   |      |

|      | vebs, (b) distinguishing svebs from non-svebs, and (c) distinguishing the |      |

|      | five aami heartbeat classes                                               | 95   |

# CHAPTER I INTRODUCTION

#### 1.1 Evolvable Hardware

Evolvable hardware (EHW) is a one particular type of hardware whose architecture/structure and functions change dynamically and autonomously in order to improve its performance in performing certain tasks [1]. By contrast to the conventional hardware machines that the structures are irreversibly fixed during design processes, the evolvable hardware machines can adapt to changes in the field or in environments. In recent years, the emerging of the EHW research has been contributed by the progress in reconfigurable hardware and evolutionary computation [1]. The adaptability of EHW machines is performed by reconfigured its own hardware structure dynamically and autonomously by the mean of evolutionary algorithms.

One of the key motivations behind EHW is to learn or adapt itself in environments. Even being in an unknown environment, the EHW devices can adapt and provide the appropriate function intelligently. This vision for a new kind of hardware devices may have not been accomplished nowadays [2]. However, with the progress on EHW research and contribution from EHW researchers around the world, the ultimate goal of intelligent and adaptive hardware could be accomplished in the near future. This thesis is a part of this EWH research community.

Relatively new research field as it is, EHW has delivered some solutions to opened question of the real-world problems. There are real-world needs for evolvable hardware, which are still opened research problems. These are adaptive computing, adaptive signal processing, adaptive communication, adaptive fault-tolerant computing, and adaptive and autonomous devices for space exploration.

## 1.1.1 Evolvable Hardware: Basic Concepts

The integration of evolutionary computation and configurable hardware devices is the key to adaptability of EHW since the objective of evolvable hardware is the "autonomous" reconfiguration of hardware structure in order to improve performance [1]. The capacity for autonomous reconfiguration with evolvable hardware makes it

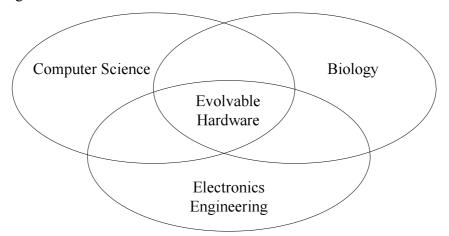

fundamentally different from conventional hardware, where it is almost impossible to change the hardware's function once it is manufactured. While configurable hardware devices, such as a Programmable Logic Device (PLD) and Field Programmable Gate Array (FPGA), allow for some functional changes after being installed on a printed circuit board, such changes cannot be executed without the intervention of human designers (i.e., the change is not autonomous). With the use of evolutionary computation, however, evolvable hardware has the capability to autonomously change its hardware functions. Figure 1.1 shows the overview of the EH research field which lies between the computer science (evolutionary computation), and electronics engineering.

Figure 1.1: Overview of Evolvable Hardware

Although there are different views on what EHW is. In this thesis, we support the view of EHW as hardware that capable of online adaptation through adapting its structure and functions dynamically, and autonomously. Our view is different to the view of EHW as a way of using evolutionary algorithms to circuit synthesis [3]. The evolutionary design of electronic circuits has been around for a long time, especially for logic and circuit synthesis [3]. The evolutionary algorithms have been used to optimize certain processes in electronics design automation such as electronics board layout and VLSI placement and routing.

The origins of our focused evolvable hardware can be traced back to two papers by Daniel Mange [4, 5] and a paper by Tetsuya Higuchi [6]. Mange's research led to bio-inspired machines that aim at self-reproduction or self-repair of the hardware structure rather evolving new structures [7, 8], the Higuchi's work targeted evolvable

hardware research utilizing genetic algorithms (GAs) for the autonomous reconfiguration of hardware structure [9, 10]. This dissertation focuses primarily on the GA-based evolvable hardware.

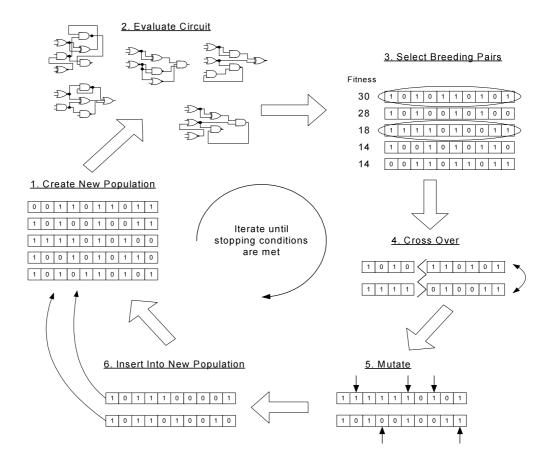

The key concept of the evolvable hardware is to regard the configuration bits of programmable hardware architecture as the chromosomes of GAs. By designing a fitness function to achieve a desired hardware function, the GA becomes a means of autonomous hardware configuration. Configuration bits "evolved" by the GA are repeatedly downloaded into the programmable hardware devices until the evolved hardware performance is satisfactory in term of fitness function values. This evolving process by GA is illustrated in Figure 1.2. From Figure 1.2, in the first step, new population, which represents different topology of circuits, are generated. Then, the circuits are measured for their performance. The GA bits that represent the circuits with higher performance are selected to be parents of the next population. By performing GA operators: crossover and mutation, the new population are generated.

A GA for evolvable hardware is executed either outside or inside the evolvable hardware, depending on its purpose. For example, if the speed of hardware reconfiguration is an important factor which is the case for intrinsic or online evolvable hardware, then GA should be a part of the evolvable hardware.

EHW can be classified into two categories: extrinsic and intrinsic EHW [3]. Extrinsic EHW simulates evolution by software running on an external computer and only downloads the best configuration to hardware in each generation or only once. Intrinsic EHW simulate evolution directly in its hardware, every chromosome will be used to configure the hardware.

There are a number of methods and techniques that propose the Genetic Algorithm (GA) and Evolutionary Algorithms (EA) to be implemented in hardware for intrinsic EHW, especially implement into FPGAs or other reconfigurable devices [11, 12]. However, intrinsically on-line evolving in hardware and to utilize hardware resource efficiently pose a challenging question of how to modify or invent efficient and improve GA or EA algorithms that can be effectively implemented into hardware.

Figure 1.2: Genetic Algorithms as a mean for hardware evolution

In addition, regarding to the increasing of density and price per performance of current FPGAs due to advanced semiconductor process technology [13, 14], there is an opportunity for designers and researchers to use higher density and faster FPGA devices for EHW at reasonable cost. Considering this trend of FPGA technology development, the concept of implementing a group of parallel processing units for EHW into a single or array of FPGA chips are feasible. In this thesis, the concept of parallel genetic algorithms will be explored.

# 1.1.2 Applications of EHW

Through many years of EHW research, the application of EHW can be classified into three main categories, namely, EHW controllers, EHW recognizers and classifiers, and EHW as optimizers for other problems. These three EHW can be summarized as follows:

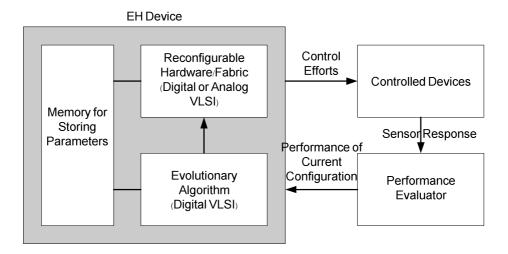

a) EHW Controllers. The EHW can be used as intelligent controllers for robots or other devices [8]. The typical EHW controller is shown in Figure 1.3.

Figure 1.3: A typical EH device for control application.

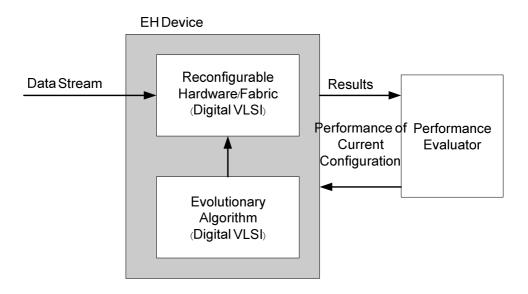

b) EHW recognizers and classifiers. EHW is capable of performing classification on streams of data at faster data rate and lower power consumption. The adaptability of EHW provides flexibility and autonomous behavior to traditional classifiers. Figure 1.4 shows the typical EHW classifiers.

Figure 1.4: A typical EH device for online classification

c) EHW as optimizers for other problems. This class of EHW is for other EHW that can not be classified into EHW controllers and EHW classifiers. There are some research projects that use evolutionary algorithm integrated hardware to provide solution to specific problems [15].

# 1.2 From Genetic Algorithms to Probabilistic Model-Building Genetic Algorithms

# 1.2.1 Genetic Algorithms

Genetic algorithms (GAs) [16, 17] are stochastic optimization methods inspired by natural evolution and genetics. GAs approaches optimization by evolving a population of candidate solutions with the operators inspired by natural evolution and genetics. Maintaining a population of solutions, as opposed to a single solution, has several advantages. Using a population allows a simultaneous exploration of multiple basins of attraction. Additionally, a population allows for statistical decision making based on the entire sample of promising solutions even when the evaluation procedure is affected by external noise.

Genetic algorithms represent candidate of solutions as binary strings to vectors of real numbers, to permutations, or even to production rules. There is no strict restriction on representations. However, most GAs uses binary strings representation for each candidate of solutions. The performance of each candidate solution is represented by a real number called *fitness*. The task of GAs is to find the binary string with the highest fitness.

The first population of candidate solutions is usually generated randomly with a uniform distribution over all possible solutions. Each iteration starts by selecting a set of promising solutions from the current population based on the performance of each solution by using various selection operators. There are two methods commonly used: tournament selection and truncation selection. In this thesis tournament selection is preferred. Tournament selection iteratively selects one solution at a time by first choosing a random subset of candidate solutions from the current population and then selecting the best solution out of this subset. Once the set of promising solutions has been selected, new candidate solutions are sampled by applying recombination (crossover) and mutation to the promising solutions. Recombination combines subsets of promising solutions by exchanging some of their parts; mutation perturbs the recombined solutions slightly.

Figure 1.5: An illustrative two types of two-parent crossover operators.

In one-point crossover, the tails are exchanged after a randomly chosen position. In uniform crossover, the bits on each position are exchanged with probability 50%. For example, one-point crossover first randomly selects a single position in the two strings and exchanges the bits on all the positions after the selected one (see Figure 1.5 (a)). On the other hand, uniform crossover exchanges bits on each position with probability 50% (see Figure 1.5 (b)).

## 1.2.2 Probabilistic Model-Building Genetic Algorithms: concepts

Probabilistic model-building genetic algorithms (PMBGAs) use probabilistic modeling of promising solutions to guide the exploration of the search space instead of using the traditional recombination and mutation operators of simple GAs [18, 19]. There are many ways of estimating the probability distribution of promising solutions and each PMBGA deals with the problem of estimating distributions in its own way.

```

(1) set t := 0

randomly generate initial population P(0)

(2) select a set of promising string S(t) from P(t)

(3) estimate the probability distribution of the selected set S(t)

(4) generate a set of new strings O(t) according to the estimate

(5) create a new population P(t+1) by replacing some strings from P(t) with O(t) set t := t + 1

(6) if the termination criteria are met, go to (2)

```

Figure 1.6: Pseudo-code of the general PMBGA procedure.

The general procedure of PMBGAs is similar to that of GAs. The initial population of PMBGA is generated at random. In each iteration, promising solutions

are first selected from the current population of candidate solutions. The true probability distribution of the selected solutions is then estimated. New candidate solutions are then generated by sampling the estimated probability distribution. The new solutions are then incorporated into the original population, replacing some of the old ones or all of them. The process is repeated until the termination criteria are met. The pseudo-code of the PMBGA procedure is shown in Figure 1.6. The difference between PMBGAs and traditional GAs is in the way PMBGAs process a population of promising solutions to generate new candidate solutions. Instead of performing crossover on pairs of selected solutions with a certain probability and then applying mutation to each of the resulting solutions, the following two steps are performed [20]:

- 1. Model building. A probabilistic model of promising solutions is constructed.

- 2. Model sampling. The constructed model is sampled to generate new solutions.

PMBGAs differ in how they cope with the above two steps and in whether they incorporate special selection or replacement mechanisms for processing the populations of solutions. In the literature, PMBGAs are also called estimation of distribution algorithms (EDAs).

#### 1.2.3 Parallel Genetic Algorithms

In order to increase the GA's efficiency, the parallelization of GA has been the active research topic using high performance computer systems [21, 22]. The parallelized GA (PGA) can be categorized into four approaches. These are global, coarse-grained, fine-grained, and hybrid approaches.

- 1) Global parallelization In this class of model, there is only one group of population. The evaluation of individual and execution of genetic operators are performed in parallel. The evaluation can be parallelized by assigning a group of individuals to a processor node to evaluate and send the results back to the common shared memory or a master node. There is no communication between each processor that evaluates each individual.

- 2) Coarse grained parallelization This is the popular model for the parallelized GAs. The whole population is partitioned into sub-populations. Within each sub-

population, individuals can only mate with others in their own sub-population. However, there is an introduction of migration operator the send some individuals from a local sub-population to other sub-population. There are key parameters for this model: topology, migration rate, and migration interval. The topology defines how each sub-population connects to other sub-populations. The migration rate and migration interval specify how many individuals in each sub-population are migrated and how often they are migrated.

- *3) Fine grained parallelization* The whole population is divided further into even smaller sub-population than the coarse grain model. The ideal case is each individual handled by only one processor node. This ideal case rarely happens in real world implementation in high performance computer systems excepting the implementation into special hardware bit-level. In summary, this model is similar to the massively parallel processors

- 4) *Hybrid parallelization* This approach is to combine two approaches to solve more difficult problems. For the coarse grained and fine grained approaches, in order to exchange individuals between each sub-population, the question of how to communicate and how costly in term of resources need to be considered. These problems are related to migration parameters: topology, migration interval and migration rate.

# 1.3 Thesis Objectives

There are five primary objectives in this thesis:

- (1) Design a new parallel genetic algorithm capable of feasible hardware implementation.

- (2) Extend the proposed algorithm to the hardware implementation

- (3) Test the developed algorithm on the designed class of problems

- (4) Design an evolvable hardware based-on the proposed algorithm

- (5) Test the designed evolvable hardware on a class of problems and real-world applications.

## 1.4 Contributions

This thesis has made the following contributions:

- (1) Proposed the cellular compact genetic algorithm (CCGA), a new parallel genetic algorithm and its hardware architecture for evolvable hardware.

- (2) Proposed an evolvable hardware based-on CCGA and block-based neural network (BBNN) to form an evolvable hardware machine.

- (3) Proposed using CCGA and BBNN as an evolvable hardware to online heartbeat monitoring and classification.

Specifically, the thesis proposes the cellular compact genetic algorithm (CCGA) and its integrating with block-based neural network (BBNN) to form evolvable hardware machines. Classified as a kind of parallel estimation of distribution algorithms, the CCGA uses the improved compact genetic algorithm with probability model migration. BBNN is an evolutionary neural network in which evolution is another form of adaptation in addition to learning. CCGA and BBNN hardware architecture are proposed. The parallel hardware architecture for integrating CCGA and BBNN presents a class of evolvable hardware.

Empirical evidence is provided to show that CCGA is capable of solving problems decomposable into sub-problem with growing difficulty and in scalable manner.

#### 1.5 Dissertation layout

The thesis is divided into six chapters. The first chapter introduces genetic algorithms, and the basic concepts of probabilistic model-building genetic algorithms (PMBGAs). Chapter II presents the related work to the thesis. Chapter III presents the cellular genetic algorithm (CCGA) and its hardware implementation. Chapter IV presents the evolvable hardware based on CCGA and block-based neural network (BBNN). Chapter V motivates the use of the proposed evolvable hardware to solve the real-world problem of ECG signal classification. The thesis closes by presenting experimental results on two classes of real-world problems, discussing interesting topics for future work, and providing the conclusions. The following subsections present the content of each chapter in greater detail.

#### 1.6 Publications

This thesis has made following publications:

- (1) Y. Jewajinda and P. Chongstitvatana, "A cooperative approach to compact genetic algorithm for evolvable hardware," Proc. IEEE Congress on Evolutionary Computation, Vancouver, Canada, 2006, pp. 624–629.

- (2) Y. Jewajinda and P. Chongstitvatana, "Cellular Genetic Algorithm for Evolvable Hardware", ECTI International Conference, Thailand, 2008.

- (3) Y. Jewajinda and P. Chongstitvatana, "FPGA Implementation of a Univariate Estimation of Distribution Algorithm and Block-based Neural Network as An Evolvable Hardware", IEEE World Congress on Computational Intelligence, Hong Kong, June, 2008.

- (4) Y. Jewajinda and P. Chongstitvatana, "FPGA Implementation of a Cellular Genetic Algorithm, NASA/ESA international conference on Adaptive hardware and Systems (AHS-2008), Netherland, July, 2008.

- (5) Y. Jewajinda and P. Chongstitvatana, An Adaptive Hardware Classifier in FPGA based-on a Cellular Compact Genetic Algorithm and Block-based Neural Network", International Symposium on Communications and Information Technology (ISCIT 2008), Vientiane, Laos, October, 2008.

# CHAPTER II LITERATURE REVIEWS

#### 2.1 Evolvable Hardware: Vision and Motivation

One of the major goals of computation intelligence research is to create method and systems that strive towards human level intelligence. Human level intelligence is manifested through adaptive learning, associative memory, pattern recognition, language communication, concept formation, abstract thinking, common sense of knowledge, consciousness [23]. So far, the methods of computational intelligence research have been successfully used in creation of some elements of human intelligence, but not for the creation of human level intelligent machines. We need to gain more knowledge to enable us to achieve a higher-degree of the intelligence in machines. Two approaches to such high level of intelligence are to understand evolving processes of the learning brain and biological organisms. Understanding human intelligence in brain allows us to implement machines closer to the human-level intelligence. In addition, understanding the development process of biological organisms allows us to create machines that capable of cellular differentiation and cellular division which are key mechanism of living organisms.

The brain is a dynamic information processing system that evolves its structure and functionality in time through information processing at different hierarchical levels. The term "evolving" is mainly concerned with the development of the structure and functionality of the individual system during its lifetime. Understanding of the interaction through its modeling is the key to comprehend information processing in brain and perhaps the brain as a whole. Building computation models that integrate principles from brain based on connectionist learning may be well towards constructing intelligence machines. These models can be called evolving connectionist system.

The majority of living creatures, with exception of uni-cellular organism, share a common multi-cellular structure in which the organism is divided into a finite number of cells and each group realizing a single function such as muscle, neuron, etc. The process that allows organisms to develop from a single initial cell to a fully-grown individual relies essentially on two mechanisms: cellular division and cellular

differentiation. The developing process of cells can inspire us to create artificial machines that are capable of these two key mechanisms. Since the bio-organisms inspire us to create hardware machines that imitate living organisms, we can call this type of machines: bio-inspired machines.

## 2.1.1 Evolving connectionist system

Evolving connectionist system is an adaptive, incremental learning and knowledge representation system that evolves its structure and functionality, where in the core of the system is connectionist architecture and that consists of neurons and connections between them. Evolving connectionist model operates continuously in time and adapts their structure and functionality through a continuous interaction with environment and with other systems. The adaptation can be defined through:

- 1. A set of evolving rules

- 2. A set of parameters that are subject to change during system operation

- 3. An incoming continuous flow of information, possibly with unknown of distribution

- 4. Goal criteria that are applied to optimize the performance of the system over time

Evolving connectionist system presented in this thesis is based-on principles from the human brain. It is known that the human brain develops before the child is born. During learning the brain allocates neurons to respond to certain stimuli and develop their connections. Some parts of brain develop connections and also retain their ability to create neurons during person's lifetime.

Adaptive learning and behaviors are keys of human level intelligence. Until recently, most researches on machine intelligence have been carried on in software domain operated on fixed hardware. The emerging field of evolvable hardware and adaptive hardware promise to deliver elements of machine intelligence at hardware level. Principles of brain development and learning can be used as inspiration for the development of evolvable hardware based-on evolving connectionist system:

- 1. Evolution is achieved through both genetically defined information and learning

- 2. The evolved neurons in the brain have a spatial-temporal representation where similar stimuli activate close neurons

- 3. Evolving through interaction with the environment

- 4. The evolving process is continuous and life long

- 5. Redundancy is the evolving process in brain leading to the creation of a large number of neurons involved in each learning tasks

Evolvable hardware based-on evolving connectionist system can be proposed as part of the classical evolvable artificial neural networks. Traditionally, evolving connectionist system is based-on software implementation. However, the concept of evolving connectionist system can be applied towards building machine intelligence at hardware level. Since most of evolving connectionist system is implemented in software running on top of the fixed hardware. There opened research opportunities for us to build an adaptive and learning aim at human intelligence level in silicon-based hardware devices.

## 2.1.2 Bio-inspired Hardware Model

As mentioned in the previous section, the developmental process of biological organisms exploits essentially two mechanisms: cellular differentiation and cellular division.

*Cellular division* is the process through which each cell achieves its duplication. During this phase, a cell copies its genetic material (i.e. the genome) and splits into two identical daughter cells.

*Cellular differentiation* defines which function a cell has to realize. This specialization, which essentially depends of the cell's position in the organisms, is obtained through the expression of a part of the genomes.

In order to implement cellular division, new approaches have to be explored and invented for the current hardware technology mainly silicon-based hardware. However, to directly implement cellular division in silicon-based system is not possible. An alternative way is to implement it at logical structures instead of physical level. This is the same concept used in field programmable logic devices (FPGAs). There are many approaches to implement cellular division and differentiation. The notable are self-replicating and embryonic approaches.

# 2.1.3 Evolvable Hardware Based-on Evolving Connectionist System and Bioinspired Machines.

The potential of evolvable hardware is its capability to adapt or change its behavior and improve its performance while executing in real physical environment. Acquiring knowledge from the evolving connectionist system and bio-inspired approach provide solid models for realization of the innovative evolvable hardware. Typical design of evolvable hardware from evolving connectionist system and bio-inspired machines has to address following issues:

- Genotype-phenotype mapping. It is common knowledge that the information stored in the genome is not sufficient to completely define the structure of the organisms. The current research suggests that genotypes code instructions on how the cells grow. The codes are interpreted the help of applying evolutionary mechanism to their design. The complex genotype-to-phenotype mapping allows reduction in size of the genome, with a consequence increase in its evolvability.

- *Structural adaptation*. Networks of neuron or cells that adapt or self-organize structurally to the environment by adding and removing neurons and connections in the system exploit mechanisms that are similar to the those used in the growth of an organism.

- *Unknown environmental adaptation*. Environment-directed adaptation and development occurs in bio-organisms. Mostly, currently implemented systems, hardly implemented in hardware, only adapt themselves with existed fixed-structure or known environment.

- Online Adaptation. The online adaptation means adaptation while the hardware is executing in a real physical environment. In a sense, it can be view as real-time adaptation. Online adaptation requires the adaptive hardware to learn incrementally and responsively. Such requirements do not seem to be met by population-based evolutionary learning. The current algorithms have limitation of re-learning the new and the old information in order to response to the new changed environment. In addition the evolutionary learning tend to require more time to reach the optimum solutions.

- Disaster Prevention in Real-time online adaptation. The risk of trial and error of the evolutionary algorithms can create severe damages to physical devices or other devices under control by the adaptive/evolvable hardware.

- Adaptation to a high-level specification of intended function. The true useful adaptive systems have to adapt themselves to provide functional without giving details. That is they have to provide users-friendly in setting new high-level adaptation objective.

- Minimal overhead for adaptation. The adaptive hardware/systems have to require low overhead in term of limited or expensive resources: times and spaces

- *Timely Adaptation*. Adaptation process has to be as fast as needed and deliver rapid reactions.

- Decision making at hardware level. So far, evolvable and adaptive hardware systems do not implement decision making process. The nowadays systems tend to implement the decision process in software for system-level adaptation.

- Hardware change autonomously apart from software. Most current implemented system. The hardware handles command sent by software module in order to perform adaptation to software-set objective. The goal is to allow hardware to adapt by interacting with environment directly and then inform software.

- New model for integrating software and evolvable/adaptive hardware.

Traditional and successful model is in the form Von-Neumann machine in which the hardware provides instruction sets for programmer to create software to control the hardware. With more intelligence and adaptive hardware, the new model of interface between hardware and software can be proposed.

- *Generalization*. Generalization is a key issue for any learning system. How well of the learning capability of the adaptive/evolvable hardware upon the unknown environment or inputs.

#### 2.1.4 Dualism of Evolvable Hardware

It can be observed that there is a kind of dualism in the various proposed evolvable hardware. The dualism consists of a network of topology and a learning algorithm. The network of topology can consists of simple or complex processing elements. The network of topology can support adaptation at its processing unit and its topology or the way they are interconnected. This dualism in a sense is analogous to hardware and software in current computing machines. In order to evolve or adapt efficiently, the learning algorithm and the hardware fabric should provide flexibility to evolve which we can call evolvability. Thus, the research direction for evolvable hardware has to address both sides of this dualism. The more flexible fabric of topology and processing units, the more powerful functions will be derived from the learning algorithm.

## 2.1.5 Evolutionary Artificial Neural Network and Evolvable Hardware

Evolutionary Artificial Neural Network (EANN) is a special class of artificial neural network that uses evolutionary algorithm to search for its parameters [24]. EANN is a model of evolving connectionist systems (ECOS) [23, 24]. According to, an ECOS is an adaptive, incremental learning and knowledge representation system that evolves its structure and functionality, where in the core of the system is a connectionist architecture that consists of neurons (information processing units) and connections between them. EANN employs the evolutionary algorithms to find important parameter of ANN such as weights, connections, learning rules. In other words, EANN can be a type of EHWs.

The simple model of ANN is the feed forward neural networks. Architecture of feed forward ANN is shown in Figure 2.1. ANN consists of a group of processing element called neuron or nodes. ANN can be described by a transfer functions in the form:

$$y_j = f\left(\sum_{i \in I} w_{ij} x_i + b_j\right), j \in J$$

(1)

Where  $y_i$  is the output node i,  $x_i$  is the input, and  $w_{ij}$  is the connecting weight between nodes i and j.

Figure 2.1: Feed forward Artificial Neural Network.

Optimizing the weights of ANN has been traditionally performed using training algorithm such as back-propagation (BP) and conjugate gradient [25]. BP has drawbacks due to its use of gradient descent [26] so it often get trapped in a local minimum of the error function and is incapable of finding minimum if the error function is multimodal and/or non-differentiable. Evolutionary Algorithm (EA) has been proposed to optimize weights of ANNs [27-30].

In this thesis, a special class of ANN called *Block-Based Neural Network* (BBNN) is introduced to be integrated with our proposed genetic algorithm to form evolvable artificial neural network (EANN) [31]. The BBNN consists of a two-dimensional (2-D) array of basic neural-network blocks with integer weights for easier implementation using reconfigurable hardware such as field programmable logic arrays (FPGAs).

BBNNs are represented by fixed-length binary codes, which correspond to network configuration bit strings of FPGAs to determine internal structures. The structure and weights of the BBNN are encoded as a 2-D chromosome for easier partial on-line reconfiguration. A genetic algorithm can evolve configuration bit strings to search for an optimal structure and weights setting of the BBNN among many possible choices of structure and weight combinations.

# 2.2 Evolvable hardware: Survey

Yao and Higuchi [2] wrote a good survey paper for evolvable hardware, they describe two difference classes of evolvable hardware (EH): evolvable hardware used as alternative for circuit design and evolvable hardware as online adaptive hardware. To achieve online adaptation, evolvable hardware must adapt its architecture while operating in real environment. Many new issues arise when online adaptation is required. This section presents a survey on new development of the field.

The first evolvable hardware chip developed for myo-electric hand control is described in Kajitani et.al [32]. Sakanashi, et al. developed GA-based EHW applied to image compression [33]. Korenek *et al.* have developed and evaluated a specialized architecture to evolve relatively large sorting networks in an ordinary FPGA [34].

Some new and practical applications have also been studied. Martinek et al. have proposed an evolvable image filter that was completely implemented in an FPGA [35]. The system is able to evolve an image filter in a few seconds. Smith et al. [36] have presented an application of GA to evolve new spatial masks for nonlinear image processing operations, which are ultimately to be implemented to evolvable hardware.

Digital evolvable hardware has also been applied to evolving robot controllers. Kim et al have shown that their proposed GA guarantees satisfactory smooth and stable walking behavior in an experiment involving a real biped robot [37].

Stefatos investigated the problem of evolvable FIR digital filter [38]. Using reconfigurable arithmetic architecture evolving with evolutionary algorithms provides promising solution over traditional design [39].

# 2.3 Probabilistic Model-Building Genetic Algorithms

This section reviews PMBGAs proposed in the past. The methods are classified according to the underlying representation of candidate solutions and the complexity of the class of models they consider. The algorithms that use a probabilistic model are also called the estimation of distribution algorithms (EDAs). There are generally three classes of EDAs that can be applied to problems with solutions represented by fixed-length string over a finite alphabet. The algorithms are classified according to the complexity of the class of models they use [40].

## 2.3.1 Without Dependency

The basic approach is to assume that the variables represent the distribution of solutions are independent. Figure 2.2 shows the graphical model with no interaction

among the variables. There are three key EDAs within this class: population-based incremental learning (PBIL) algorithm [41], univariate marginal distribution algorithm (UMDA) [42], and compact genetic algorithm (cGA) [43].

Figure 2.2: Graphical models with no interactions

In the univariate marginal distribution (UMDA), the probability model is represented as factorized of a product of independent univariate marginal distributions. That is:

$$p_l(x) = p(x|D_{l-1}^{Se}) = \prod_{i=l}^{n} p_l(x_i)$$

(2.1)

$D_0 \leftarrow$  Generate *M* individuals (the initial population) at random

**Repeat** for l = 1, 2, ... until the stopping criterion is met

- 1.  $D_{l-1}^{Se} \leftarrow \text{Select } N \leq M \text{ individuals from } D_{l-1} \text{ selection}$  method

- 2. Estimate the joint probability distribution

$$p_l(X) = p(X|D_{l-1}^{Se}) = \prod_{i=1}^{n} p_l(x_i)$$

3. Generate a new population  $D_l \leftarrow \text{Sample } M \text{ individuals from } p_l(X)$

Figure 2.3: Pseudocode of UMDA

$D_l^{Se}$  is the current data file containing selected individuals of generation l in which each  $D_{l-1}^{Se}$  contains many cases of patterns of "one" and "zero". Table 2.1 shows an

example of  $D_l^{Se}$ . Each univariate marginal distribution is estimated from marginal frequencies:

$$p_l(x_i) = \frac{\sum_{j=1}^{N} \delta_j(X_i = x_i | D_{l-1}^{Se})}{N}$$

(2.2)

Where

$$\delta_j(X_i = x_i | D_{l-1}^{Se}) = \begin{cases} 1 \text{ if in the j}^{th} \text{case of } D_{l-1}^{Se}, X_i = x_i \\ 0 \text{ otherwise} \end{cases}$$

(2.3)

Table 2.1: An example of  $D_l^{Se}$

|   | X1 | X2 | X3 | X4 |

|---|----|----|----|----|

| 1 | 1  | 0  | 1  | 0  |

| 2 | 0  | 1  | 0  | 1  |

| 3 | 1  | 0  | 0  | 0  |

| 4 | 1  | 1  | 0  | 1  |

Obtain an initial probability vector:

$$p_0(X) = (p_l(x_1), \dots, p_l(x_i), \dots, p_l(x_n))$$

while no convergence do

#### begin

- 1. Using  $p_l(x)$  obtain M individuals:  $x_1^l, \dots x_k^l, \dots, x_M^l$

- 2. Evaluate and rank  $x_1^l$ , ...  $x_k^l$ , ... ,  $x_M^l$

- 3. Select the  $N (N \le M)$  best individuals

- 4. Update the probability vector

**For**

$$i = 1, ... n do$$

$$p_{l+1}(X_i) = (1-\infty)p_l(x_i) + \infty \frac{1}{N} \sum_{k=1}^{N} x_{i,k:N}^l$$

end

Figure 2.4: Pseudocode of PBIL

Population-based incremental learning (PBIL) algorithm represents the solution by binary string of fixed length. In PBIL, population of solutions is replaced by the probability vector which is initially assigned each value of each position in the vector to the same probability at 0.5. Each generation the probability vector is shifted towards the desired solutions by using Hebbian learning rules [41]. Figure 2.4 shows the pseudocode of PBIL.

The compact GA (cGA) represents the population with a single probability vector. The pseudocode of the compact GA is shown in Figure. 2.5. At each generation, the two individuals are randomly generated from the probability vector. Then, tournament selection is performed over the two individuals. Each bit of the probability vector is adjusted according to the result of the competition. Eventually, the CGA keeps running until the probability vector is converged.

```

1. Initialize probability vector

p(X) = (p_l(x_l), ..., p_l(x_i), ..., p_l(x_n))

= (0.5, ..., 0.5, ..., 0.5)

```

2. Generate two individuals from the vector p(X)

3 Let them compete

winner,

$$loser = evaluate(a, b)$$

4. Update the probability vector toward the *winner*

5. Check if the probability vector has converged

for

$$i := 1$$

to  $n$  do

if  $p[i] > 0$  and  $p[i] < 1$  then goto step 2

6. p(X) represents the final solution

Figure 2.5: Pseudocode of compact GA

## 2.3.2 Pairwise Dependency

By taking dependency between a pair of variables, there are three key algorithms in this class. The mutual information-maximizing input clustering (MIMIC) algorithm, a dependency tree approach proposed, and the bivariate marginal distribution algorithm (BMDA) are key algorithm for pairwise dependency [44]. Figure 2.6 demonstrates the difference of these three algorithms in term of graphical model.

Figure 2.6: Graphical model of pairwire dependency algorithms

The mutual information-maximizing input clustering (MIMIC) algorithm which uses a simple chain distribution as shown in Figure 2.5. MIMIC employs greedy search approach to search in each generation for the best permutation of variables to construct a chain of variables. In this fashion the Kullback-Liebler divergence between the chain and the complete joint distribution is minimized. Since MIMIC uses only a greedy search algorithm, therefore global optimality of the distribution is not guaranteed.

Baluja and Davies [41] use dependency trees to model promising solutions (see Figure 2.5). Similarly as in the PBIL, the population is replaced by a probability vector which contains all pairwise probabilities. The probabilities are initialized to 0.25 and repeatedly adjusted according to new promising solutions acquired on the fly. Estimation of the probability distribution of the selected individuals in each generation is done using a tree structured Bayesian network with a learning algorithm proposed by Chow and Liu [41]. Once the probabilistic model is derived, individuals of population are sampled from it. There are two major advantages of using trees instead of chains. Trees are more general than chains because each chain is a tree.

Moreover, by relaxing constraints of the model, in order to find the best model (according to a measure decomposable into terms of order two), the global optimality of the solution can be derived.

The bivariate marginal distribution algorithm (BMDA) uses a set of dependency graph that need only second-order statistics [41]. A set of dependency graph is similar to a set of trees that not mutually connected. This class is even more general than dependency trees approach because the a dependency tree is a set of dependency graph. Pearson's chi-square test is used to determine which pair of variables should be connected and to construct the final mode. In each generation the factorization obtained with the BMDA is given by:

$$p_{l}(X) = \prod_{x_{r} \in R_{l}} p_{l}(x_{r}) \prod_{x_{i} \in V \setminus R_{l}} p_{l}(x_{i} | x_{j(i)})$$

2.4

where V is the set of n variables,  $R_l$  denotes the set containing the root variable in generation l, and  $X_{j(i)}$  return the variable connected to the variable  $X_i$  and added before  $X_i$ . The probabilities for the root nodes,  $p_l(x_r)$  and the conditional probabilities,  $p_l(x_i|x_{j(i)})$  are estimated from database,  $D_{l-1}^{Se}$ , containing selected individuals.

#### 2.3.3 Multivariate dependencies

For difficult problems with multivariate or highly-overlapping building blocks, pairwise dependency can not solve those problems efficiently. Researchers propose to use more complex graphical model to handle such problems. However, using more complex model tend to increase computing time and sometimes still do not guarantee global optimality of the resulting probabilistic models. In this section, the extended compact genetic algorithm (ECGA) [44], factorized distribution algorithm (FDA), and Bayesian optimization algorithm (BOA) are presented.

ECGA groups the variables into many clusters. Each cluster is taking as a whole and different clusters are considered to be mutually independent. To discriminate models, ECGA uses a minimum description length (MDL) metric which prefers model that allows higher compression of data.

The factorized distribution algorithm (FDA) uses a factorized distribution as a fixed model throughout the whole computation. The structure of problem which is the

distribution and its factorization needs to be given by experts. Unfortunately, this usually not available when solving real-world problems, and therefore the use of FDA is limited to some specific problems.

The Bayesian optimization algorithm (BOA) models the probability using Bayesian networks. BOA uses the Bayesian Dirichlet (BD) equivalence metric to measure the quality of each network. The BD metric does not prefer simpler model to the more complex ones. It uses only accuracy as the criterion. The search for the model is done by using greedy search and it starts each generation from scratch. BOA has been continuously developed and improved [44].

## 2.4 Test Functions for Genetic Algorithms

This section presents test functions for the proposed GAs. In experiments described in this dissertation, various test problems are used to compare the experimental results with the compact GA which is equivalent to simple GAs [43]. Fitness value (e.g., the number of correct BBs) over generations of population is taken to be performance measure.

## 2.4.1 Problems Involving Lower Order BBs

A 100-bit one-max problem (i.e., the counting ones problem) and a minimum deceptive problem (MDP) (formed by concatenating ten copies of minimum deceptive function) are considered for evaluating the proposed algorithms on problems involving lower order BBs [45]. The one-max problem and the MDP are representative problems with the order-one BBs and the order-two BBs, respectively.

The MDP problem is defined by

$$f_{MDP} = \sum_{i=1}^{m} f(x_{2i}),$$

where  $f(x_{2i}) = \begin{cases} 0.7, & \text{if } x_{2i} = 00\\ 0.4, & \text{if } x_{2i} = 01 \end{cases}$  and  $f(x_{2i}) = \begin{cases} 0.0, & \text{if } x_{2i} = 10\\ 1.0, & \text{if } x_{2i} = 11 \end{cases}$  (2.5)

Here,  $x_{2i}$ , presents the value (i.e., alleles) of a 2-bit long sub-string.

## 2.4.2 Problems involving higher order BBs

Fully deceptive problems are used to test the proposed algorithms on problems involving higher order BBs. Deceptive trap functions are used in many studies of GAs because their difficulty is well understood and it can be regulated easily. The deceptive trap is defined by

$$f_{trap}(u, a, b, z, k) = \begin{cases} \left(\frac{a}{z}\right)(z - u), & \text{if } u \leq z \\ \left\{\frac{b}{(k - z)}\right\}(u - z), & \text{otherwise} \end{cases}$$

(2.6)

where u is defined as the number of ones of a sub-string, a and b are the local deceptive and the global optimum respectively, z is the slope-change location, and k is the problem size.

The first deceptive problem is based-on a three-bit trap function. The test problem is formed by concatenating thirty copies of the three-bit trap function for a total chromosome length of 90 bits. Each three-bit trap function has a deceptive-to-optimal ratio of 0.7. That is, the problem is formulated by

$$f_{3-bit} = \sum_{i=1}^{10} f_{trap}(u_{3i}, 0.7, 1, 2, 3)$$

(2.7)

where  $u_{3i}$ , is a 3-bit long string.

The second deceptive problem is 4-bit trap which is formed by concatenating thirty copies of the 4-bit trap function for a total chromosome length of 120 bits. Each 4-bit trap function has a deceptive-to-optimal ration of 0.7. That is the problem is specified by

$$f_{4-bit} = \sum_{i=1}^{10} f_{trap}(u_{4i}, 0.7, 1, 3, 4)$$

(2.8)

#### 2.4.3 Continuous and Multimodal Functions

Many real-world problems do not involve the concatenation of distinct order-k BBs in a simple manner since their solution and search space are continuous and multimodal. The problems can be modeled as an intricate combination of lower and higher-order BBs. In order to investigate the performance on such problems, a circle function and Schaffer's binary function are employed [45]. The functions maybe used for modeling several real-world problems, especially those arising in the emerging areas of wireless networks.

The circle function is investigated. It is defined in (2.9) and plotted in Figure 2.7. This multimodal function has many local optima (i.e., minima) there are located on concentric circles near the global optimal.

Minimize

$$f_c(x) = (\sum_{i=1}^n x_i^2)^{1/4} \left[ \sin^2 \left( 50 \left( \sum_{i=1}^n x_i^2 \right)^{1/10} \right) + 1.0 \right]$$

(2.9)

$x_i \in [-32.767 \ 32.768], \quad n = 2$

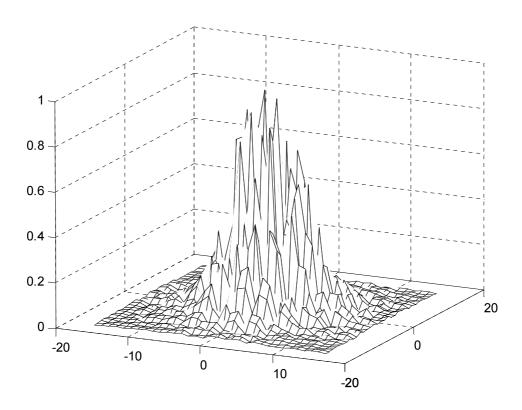

Figure 2.7: Plot of the circle function

Schaffer's binary function is presented in (2.10). The characteristic of this function are easily grasped from it two-dimensional case shown in Figure 2.8. The function is degenerate in the sense that many points share the same global optimal function value ( $f_{s6}^* = 0.99400693$ ). As can be seen in Figure 2.7, the points are located on the highest circle in the crown near the origin.

Maximize

$$f_{s_6}(x) = \frac{\sin^2\left(\sqrt{\sum_{i=1}^n x_i^2}\right)}{1.0 + 10^{-3}\left(\sum_{i=1}^n x_i^2\right)^2}$$

(2.10)

$$x_i \in [-16.383 \ 16.384], \qquad n = 5$$

Figure 2.8: Plot of the Schaffer's function with 2-D (n=2)

# 2.5 Parallel Estimation of Distribution Algorithm with Probability Model Migration

Parallel estimation of distribution algorithms or parallel probabilistic-modeling genetic algorithms is based on the traditional parallel genetic algorithms. However, the key difference is how the EDA manages probability vector instead of individuals in the population. This difference has important effects on how to parallelize the algorithms. In this section, parallel GAs or EDAs with multiple populations is in our attention since the proposed algorithm is developed from it and so many researches has been developed in this class of algorithm. This class of GAs is also called *coarse-grained* or *island model*. The design of multiple-deme parallel GAs involves

difficult and related choices. The main issues are to determine (1) the size and number of demes, (2) the topology that interconnect the demes, (3) the migration rate that controls how many individuals migrate, (4) the frequency of migration, and (5) the migration policy that determines which individuals migrate and which are replaced in the receiving demes [46, 47].

Most parallel EDAs concentrate on parallel construction and sampling of probabilistic models in order to speed up the process especially for EDAs with complex model like Bayesian optimization algorithm (BOA) [48, 49]. The idea of the multi-deme estimation of distribution algorithm (PEDAs) based on PBIL algorithm is presented in [50]. In [49], mixture of distribution with Bayesian inference is discussed. The concept of migration of probability parameters instead of individuals was firstly published in [51] where UMDA platform with the convex combination of univariate probability models is investigated for various network topologies. In [52] parallelization of compact GA is presented. Further enhancement of this concept is described in [53] where local search methods are used to identify which parts of migrant model can improve the resident model. Recently, the island model of Bivariate marginal distribution algorithm (BMDA) is presented in [54]. In [54], the unidirectional ring topology is used. The cooperation of demes is realized via migration of probabilistic models. It introduces an adaptive learning technique, based on the quality of resident and immigrant subpopulation, which consists of the adaptation of the resident by the incoming neighbor immigrant model. Using parallel EDA based-on compact GA to solve the scalability problem of GA is presented in [55].

# 2.6 Hardware Implementation of Genetic Algorithms

GA process is a time-consuming. For many real-world applications, GA can run for days, even when they are executed on a high performance workstation. To reduce the execution time of GA, several method have been offered, including parallel and/or distributed processing of GA along with its hardware implementation [56, 57]. A myriad of hardware-based GA have been proposed in recent years. The hardware-based GA can be categorized into three methods: direct implementation from the

existing genetic algorithms, parallelized hardware implementation some parts of the algorithm, and new genetic algorithms invented for hardware implementation.

The genetic algorithms and evolutionary algorithms been have implemented in hardware in three areas [58]:

- 1. A means of implementing the fitness functions of GAs.

- 2. A platform for implementing the EA/GAs for general optimization problems.

- **3.** An evolutionary engine in intrinsic evolvable hardware

## 2.6.1 Direct Hardware Implementation of the Basic Genetic Algorithms

For this approach to the hardware implementation of GA, Scott et al. proposed a hardware-based genetic algorithm (HGA), which was implemented on a set of field-programmable gate arrays (FPGAs). The HGA is based on the simple genetic algorithm (SGA) [59].

Yoshida et al. [56, 60] proposed a hardware-based GA called the GA processor (GAP). The GAP is based on a steady-state GA.

Shakleford et al. [61, 62] proposed their original GA. It was called the survival-based GA. It is somewhat similar to the steady-state GA. They implemented a complete GA system using Xilinx XCV3200E chip. Their implementation uses extensive pipelines and parallel fitness evaluation to get performance increase of 320 times when compared to the same algorithm running on a 366Mhz Pentium CPU.

Kajitani et al. [63] proposed GA hardware for evolvable hardware on a single LSI chip.

Wakabayashi et al. [64] also proposed a VLSI implementation of an adaptive GA, called the GA accelerator (GAA) chip as a general purpose GA hardware.

Yamaguchi et al. [65] used an FPGA to implement a coprocessor for evolutionary computation to solve the iterated prisoners' dilemma problem. They reported a 200 times performance speed up in processing the problem on FPGA when compared to a 750MHz Pentium processor.

Graham and Nelson [66] implemented a complete GA system using four FPGAs. Each FPGA was programmed to carry out a different function; selection, crossover, fitness, and mutation. Each FPGA passed its results to the next FPGA, forming a

pipeline GA. The performance of their system was compared to a software implementation running on a 125MHz PA-RISC workstation and they gain four times of improvement.

## 2.6.2 Parallelized Hardware Implementation of the Existing Genetic Algorithm

The early effort to implement the parallel genetic algorithm in hardware is presented in Turton et al [67]. They implemented fine-grained GA for image registration. Each processor node processes only one chromosome. The result was simulated.

Bland et al [57] implemented the genetic operators of the simple genetic algorithm in a systolic array like architecture. Also, four systolic arrays form a macropipeline which implements the operators. They proposed the implementation for a system consisted of a general purpose processor augmented with an FPGA.

Tufe and Haddow [64] designed pipeline architecture for the GA called GA Pipeline for intrinsic evolvable hardware. The main functions of GA Pipeline are selection, genetic operation, fitness and sorting which are implemented in separate modules. The pipeline consists of two phases: reproduction and updating.

Cho et al. [68, 69] proposed the genetic algorithm processor (GAP) based on subpopulation architecture. They applied the steady-state GA with modified tournamenet selection, special survival condition and the parallelism of coarse-grain GA. Their implementation keeps a group of best individual in each generation. Ring topology was proposed for interconnection. The Altera FPGA was used to implement one GAP.

Nedjah et al. [70] proposed a massively parallel architecture for hardware implementation of genetic algorithms. They implemented the fitness computation in parallel hardware units which they proposed as a hardware-based neural network. Also, the crossover, mutation and selection are implemented in parallel using multiple crossover, mutation, and selection units. However, this parallel hardware implementation still using large amount of memory because of its implementation is based on a simple genetic algorithm.

Jelodar et. al. [71] designed a parallel GA for an System-on-a-Programmable-Chip (SOPC) called SOPC-based parallel GA. The global GA which has one population was implemented in parallel hardware. The new idea in this paper was to

propose using configurable processors with genetics operators together. This approach resembles software-hardware co-design architecture for the global parallel genetic algorithm.

#### 2.6.3 New Genetic Algorithms for Hardware Implementation

To implement GA in hardware from the existing software-based genetic algorithm tends to require more hardware resources and memory. Researchers have proposed solutions to these problems by design new or modified genetic algorithms suitable for hardware implementation [58].

The compact genetic algorithm (CGA) is a probability vector-based evolutionary algorithm that can be efficiently implemented in digital hardware [72]. Even though CGA has advantage for hardware implementation, but unfortunately, the basic CGA lacks of sufficient search power for real world EH applications that require accuracy and faster processing time. Therefore, the CGA is improved by adding more techniques like elitism, mutation, and champion resampling. This modified CGA is called \*CGA or \*CGA family. Gallagher et al. [58] proposed a family of compact genetic algorithms to be implemented in hardware. They modified a basic compact GA with elitism, mutation, and resampling. The modified compact GA called \*CGA performs better than a basic compact GA with reasonable increased hardware resources. The reason behind using the compact GA is that CGA can be implemented in hardware without memory.