#### REFERENCES

- 1. Gardner R.P., and Ely R.L. Jr.: Radioisotope Measurement Application

in Engineering. Reinhold Publishing Corporation, 1967.

- 2. Lancaster D.: CMOS Cookbook. Indiana: Howard W. Sams & Co., 1977.

- National Semiconductor: CMOS Databook, National Semiconductor

Corporation, Santa Clara, CA95051

- 4. Sonde B.S.: "Power Supplies. "Monographs on Solid State Electronic

Instrumentation. TATA: McGraw. Hill Publishing Company Ltd.

1980. pp. 39-60.

- 5. Knoll G.F.: Radiation Detection and Measurement. New York: John Wiley & Sons Inc., 1979.

- 6. Hamilton T.D.S.: Handbook of Linear Integrated Electronics for

Research. London: McGraw-Hill Book Co., 1977.

- 7. Suthus Linhaphan: "Development of High Voltage Power Supply for Nuclear Radiation Detectors." Thesis, Graduate School, Chulalongkorn University, 1977.

#### APPENDIX A

#### CALCULATIONS

# A.l. High Voltage Power Supply

#### A.1.1. Inverter

Given

$$P_{\text{out}} = HV. \times I_{\text{max}} = 2.5 \times 10^3 \times 200 \times 10^{-6}$$

$= 0.5 \text{ W}$

$V_{\text{in}} = 6 \text{ V}$

$V_{\text{out}} = 650 \text{ V}$

$P_{\text{in}} = \frac{P_{\text{out}}}{\eta} = \frac{0.5}{0.8} = 0.625 \text{ W}$

$I_{\text{c}} = \frac{P_{\text{in}}}{V_{\text{in}}} = \frac{0.625}{6} = 0.104 \text{ A}$

$I_{\text{o}} = \frac{P_{\text{out}}}{V_{\text{out}}} = \frac{0.5}{650} = 7.69 \times 10^{-4} \text{ A}$

Select TR MPSU06 for  $Q_5$ ,  $Q_6$

$h_{\text{FEmin}} = 30$

$I_{\text{B}} = I_{\text{C}} = \frac{0.104}{30} = 3.46 \times 10^{-3} \text{ A}$

Since  $R_{\text{C}} + R_{\text{B}} = \frac{V_{\text{CC}} - V_{\text{BE}}}{I_{\text{E}}}$

Choose

$$R_9$$

,  $R_{10} = 220 \Omega$

$R_{C} + R_{B} = \frac{5 - 0.6}{3.46 \times 10^{-3}} = 1271.68 \Omega$

Select ferrite core TDK.P2616 H5B. pot core, which is characterized by A core = 0.95 cm<sup>2</sup>, 80 % of B sat = 3500 gauss. From N =  $\frac{V_{dc \times 10}^8}{4 f B A}$

with given

$$V_{dc}$$

= 6 V. and frequency 5  $k_{Hz}$

$$N_{p} = \frac{6 \times 10^{8}}{4 \times 5 \times 10^{3} \times 3500 \times 0.9}$$

= 9 turns

Therefore, the transformer primary turns is 18 turns center-tap.

and

$$\frac{N_p}{N_s} = \frac{V_p}{V_s}$$

$$N_s = \frac{N_p}{V_p} \times V_s$$

$$= \frac{9 \times 650}{6} = 975 \text{ turns}$$

The scondary turns is 975 turns

Select the wire size from the table

wire size of

$$T_p = 34 \text{ SWG}$$

wire size of

$$T_S = 45 \text{ SWG}$$

To keep the transistor  $Q_5$ ,  $Q_6$  saturate during the entire half cycle

$$C_4 = C_5 = \frac{T}{20R} = \frac{1}{20 \times 220 \times 5 \times 10^3} = 0.045 \,\mu\text{F}$$

Given the power dissipation on clamp circuit = 0.05  $P_{out}$  [7]

$$R_{11} = \frac{(2V_{in})^2}{0.05 P_{out}} = \frac{(2 \times 6)^2}{0.05 \times 0.5} = 480 \Omega$$

# .11

$^{\text{C}}_{6} = \frac{20\text{T}}{R_{11}} = \frac{20}{5 \times 10^{3} \times 500} =$

# A.1.2 Oscillator circuit

Select TR2N3904 with  $h_{FE}^{}$  50 as  $Q_1^{}$ ,  $Q_2^{}$

$$I_C = \frac{V_{CC}}{R_C} = \frac{5}{10 \times 10^3} = 5 \times 10^{-4} A$$

$$I_{B} = \frac{I_{C}}{h_{FE}} = \frac{5 \times 10^{-4}}{50} = 1 \times 10^{-5}$$

A

$$R_{b} = \frac{V_{CC} - V_{BE}}{I_{R}} = \frac{5 - 0.6}{1 \times 10^{-5}} = 440 \text{ k}\Omega$$

Choose

$$R_3$$

,  $R_4 = 390 \text{ k}\Omega$

For frequency 5kHz and 50% duty cycle

$$T = t_1 + t_2 = \frac{1}{f}$$

$$= 2 \times 0.693 \text{ RC}$$

$$C = \frac{1}{2 \times 0.693 \times 390 \times 10^3 \times 5 \times 10^3}$$

$$= 370 \text{ pF}$$

Choose  $C_1$ ,  $C_2 = 350 \text{ pF}$

# A.1.3 Regulator circuit

Given

$$V_{O} = 6 \text{ V}.$$

$$V_{O} = V_{L} - V_{BE}(Q_{8}) - V_{BE}(Q_{7})$$

$$V_{L} = V_{O} + V_{BE}(Q_{8}) + V_{BE}(Q_{7})$$

$$= 6 + 1.2 = 8 \text{ V}.$$

From  $E_{Q} = 2.7, V_{L} = V_{R}(1 + \frac{R_{1}}{R_{2}})$

When  $R_{2} >> R_{1}$

$$V_{R} = V_{L}$$

Given  $V_{R} = 9 \text{ V}.$

Voltage reference adjust in range of V\_BE (Q\_8) + V\_BE (Q\_7) to 9 V. i,e 1.2 V. - 9 V.

Choose  $VR_1 = 10 \text{ k}\Omega$

$$R_{13} = \frac{VR_1 V_{R13}}{V_1 - V_{R13}}$$

$$= \underline{10 \times 10^3 \times 1.2} = 1.54 \text{ k}\Omega$$

$$= 9 - 1.2$$

Choose

$$R_{13} = 1.5 \text{ k}\Omega$$

$$V_{R17} \simeq V_{R}$$

$$V_{R17} = \frac{V_{HV}^{R}_{17}}{R_{17} + (R_{14} + R_{15} + R_{16})}$$

$$(R_{14} + R_{15} + R_{16}) = \frac{V_{HV}^{R}_{17}}{V_{R17}} - R_{17}$$

$$= \frac{2.5 \times 10^{3} \times 100 \times 10^{3}}{9} - 100 \times 10^{3}$$

$$= 27.68 \text{ M}\Omega$$

Choose

$$R_{14} = R_{15} = 10 \text{ M}\Omega$$

$$R_{16} = 6.8 \text{ M}\Omega$$

# A.1.4 Positive 9 V. power supply

$$I_{R22} = I_{z min} + I_{L}$$

Current  $\mathbf{I}_{\mathbf{L}}$  consumed at + 9 V. terminal is 0.05 A

$$I_{z \text{ min}} = 0.2 I_{L} = 0.01$$

A

$$I_{R22} = 0.05 + 0.01 = 0.06 \Lambda$$

$$R_{22} = \frac{V_{SUPP} - V_{z}}{I_{R22}} = \frac{12 - 9}{0.06} = 50 \Omega$$

$$P_{z} = I_{z \text{ max}} \times V_{z} = 0.54 \text{ W}$$

Select the zener 9 V., 1 W.

$$R_{22} = 50\Omega , 1 W$$

# A.2 Amplifier Discriminator

A.2.1 Amplifier (

$$IC_1$$

,  $IC_2$ ,  $IC_3$ )

Bias the noninverting input so that the output of operational amplifier operates at 2 V above ground level.

let

$$I_{R7} + R_8 = 100 \mu A$$

$R_7 + R_8 = \frac{V_{CC}}{I} = \frac{5}{100 \times 10^{-6}} = 50 k\Omega$

$V_{R8} = 2 \text{ volt}$

$R_8 = \frac{V_{R8} \times (R_7 + R_8)}{V_{CC}}$

$= \frac{2 \times 50 \times 10^3}{5} = 20 k\Omega$

$R_7 = 50 k\Omega - 20 k\Omega = 30 k\Omega$

From Eq. 2,10 charge sensitive amplifier gain =  $-\frac{C_i}{C_f}$

$$\frac{V_o}{V_i} = -\frac{C_i}{C_f}$$

Choose

$$C_3 = 1 \text{ pF}$$

and  $C_6 = 4.7 \text{ pF}$  (NPO.)

$$R_4 = 22 \text{ M}\Omega$$

From Eq 2.13 voltage gain of inverting amplifier =  $-\frac{R_{f}}{R_{in}}$

Choose

$$R_{10} = R_{12} = 100 \text{ k}\Omega$$

and

$$R_6 = R_{11} = 10 \text{ k}\Omega$$

$$A_1 = -\frac{R_{10}}{R_6} = -\frac{100 \text{ k}\Omega}{10 \text{ k}\Omega} = -10$$

$$A_2 = -\frac{R}{R_{11}} = -\frac{100 \text{ k}\Omega}{10 \text{ k}\Omega} = -10$$

cascade gain =

$$A_1 \times A_2 = 100$$

Overall gain of Amplifier can be adjusted by a trimpot or by a fixed resistor at  ${\rm R}_{\rm f}$  of IC  $_2$

# A.2.2 Discriminator (IC4)

Bias level adjustable level from 0-2 V

Choose

$$VR_2 = 50 \text{ k}\Omega$$

given

$$V_{R13} = V_{R14} = 1.5 V.$$

$$R_{13} = R_{14} = \frac{VR_2 \cdot V_{R13}}{V_{R2}} = \frac{50K \times 1.5}{2} = 37.5 \text{ k}\Omega$$

Choose

$$R_{13} = R_{14} = 36 \text{ k}\Omega$$

and pull up resistance  ${\rm R}_{15}^{}$  = 10  ${\rm k}\Omega$

## A.3 Ratemeter and Low Voltage (LV) Power Supply

#### A.3.1 ratemeter

Time constant of meter circuit  $(\tau_1) = VR_6 C_{10}$  at 0 to 90 % of final reading

$$\tau_1 = 2 \text{ RC}$$

$$= 2 \times 50 \times 10^3 \times 100 \times 10^{-6} = 10 \text{ s}$$

Pulse width of monostable multivibrator  $IC_{1c}$ ,  $IC_{1d} = \tau_2$

$$\tau_2 = 1.3 \text{ RC}$$

$\tau_2 \ll \tau_1$  (condition of ratemeter)

given  $\tau_2$  in minimum range (VR<sub>5</sub> C<sub>9</sub>)  $\frac{\tau_1}{10}$

$$\tau_2 \simeq 10 \text{ ms}$$

Choose  $C_9 = 0.47 \mu F$

$$VR_5 = \frac{{}^{T}2}{1.3C} = \frac{10 \times 10^{-3}}{1.3 \times 0.47 \times 10^{-6}}$$

$$= 16.37 \text{ k}\Omega$$

Choose  $VR_5 = 22 \text{ k}\Omega$  for calibrated scale.

In the other ranges time constant decreses in step of ten

then

$$C_8 = 0.047 \mu F$$

$C_7 = 0.0047 \mu F$   $C_6 = 470 pF$

with

$$VR_5 = VR_4 = VR_3 = VR_2 = 22 k\Omega$$

A.3.2 LV. Supply

Select LM 340 T-5, To-220 package three terminal voltage regulator which is characterized by

Io = 500 mA , unregulated input voltage maxinum 35 V.

In ac power supply full wave rectifier

Select  $D_1$ ,  $D_2$  1N 4001 with  $I_f$  1  $A_{max}$  and PIV 400 V.

$$V_{DC} = V_{O} + V_{D}$$

$$V_{rms} = \frac{V_{DC}}{\sqrt{2}} = \frac{12 + 0.6}{\sqrt{2}} = 9 \text{ V.}$$

Secondary winding of transformer is 18 V. center-tap with  ${\rm I_L}~=~500~{\rm mA}.$

## B.1 CMOS logic gates applications

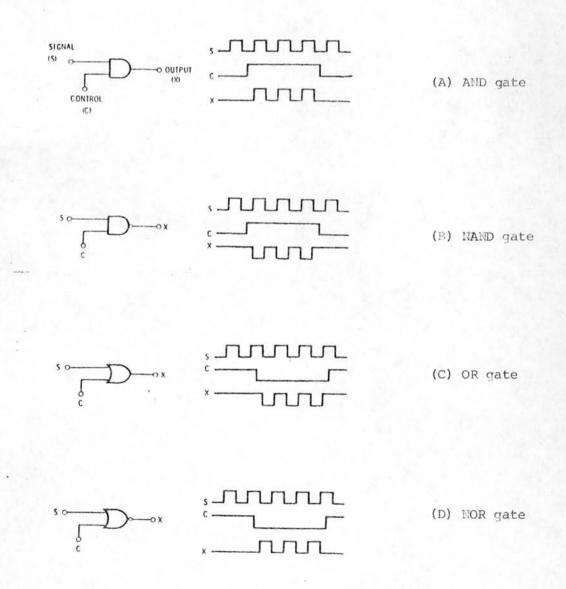

In the circuits under digital control, a train of digital pulses may be wanted to turn on or off for some purposes. In one place this might occur at the input to a counting circuit, where we would like to count the number of pulses that happen in a period of time.

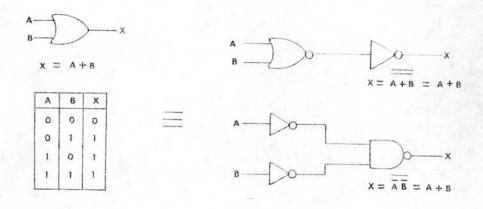

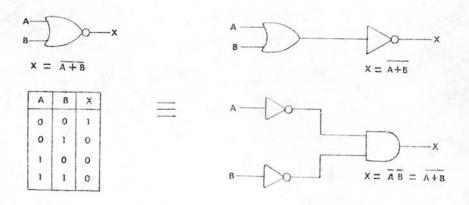

Fig. B.l shows several ways to use CMOS as a simple switch.

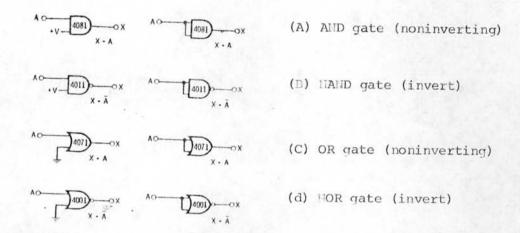

All of the two-input gates can be converted to buffer or inverter.

Fig. B.2 shows how to use the two-input direct logic functions; e.g. AND, NAND, OR, NOR, as inverter or buffer.

Fig. B.2 Converting multiple-input gates to inverters or buffers

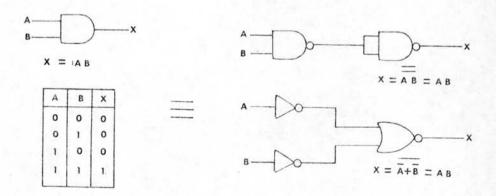

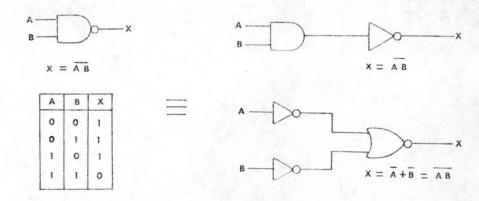

In Fig. B.3 shows several ways to build an AND, OR, NOR and NAND gate by use of the remainder gate in circuit designed.

(A) The AND gate

(B) The NAND gate

(C) The OR gate

(D) The NOR gate

Fig. B.3 Combination gates to other gate

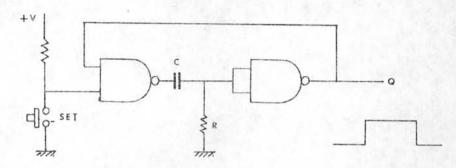

B.2.2 Monostable multivibrators or One-shot circuits are built by cross-coupling feedback between two gates to hold the unstable state of Q in the interval of RC time constant, after being triggered by the set switch. This circuit is used for debouncing contact and time delay trigger.

Fig. B.6 Monostable multivibrator built with NAND gates

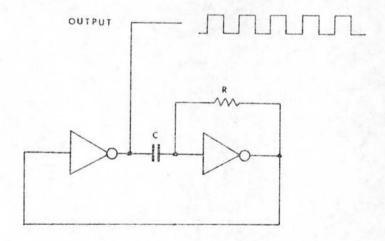

B.2.3 Astable multivibrator circuits are built by conventional resistor-capacitor charging circuits. The cross-coupling feedback network between two inverter gates produces the automatic changing state in free running. The oscillator source is formed as shown in Fig. B.7

Fig. B.7 Astable multivibrator built with inverter gates

#### B.2 CMOS Multivibrators

The multivibrators are two states circuits. These circuits become two-stated by cross-coupled feedback between a pair of inverting gates or a pair of inverters. The circuit has monostable state, bistable state and nonstable state or a statble state, depending on the feedback component.

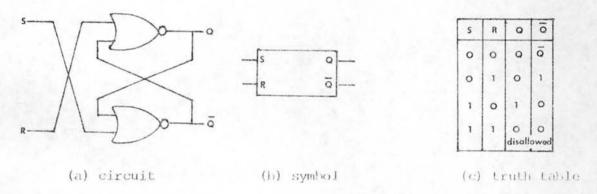

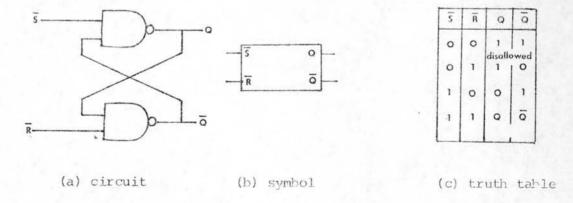

B.2.1 Bistable multivibrators or Flip-Flop circuits are built by symmetry eross-coupling at the input of the two gates. Fig. B.4 and B.5 show the simplest flip-flop which is useful for latch-condition of Q and  $\overline{\mathbb{Q}}$  in the circuit design.

Fig. B.4 Set-reset flip-flop built with NOR gates

Fig. B.5 Set reset flip-flop built with NAND gates

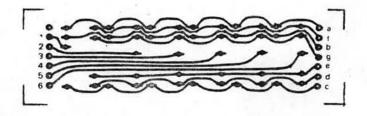

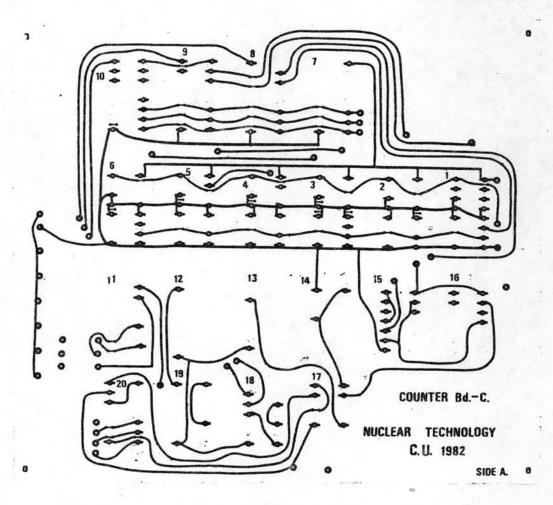

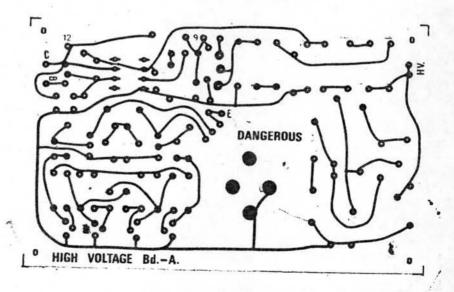

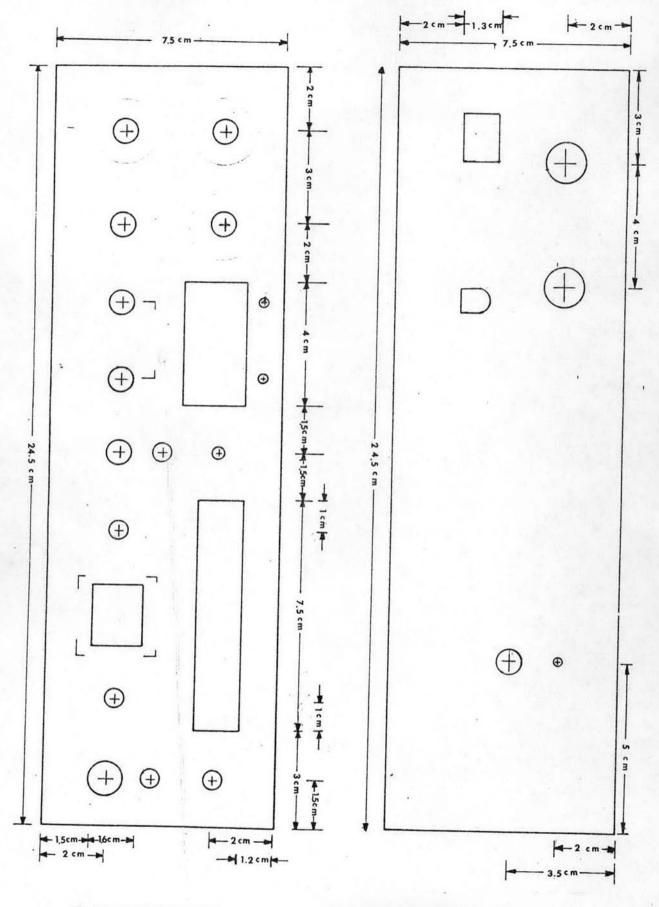

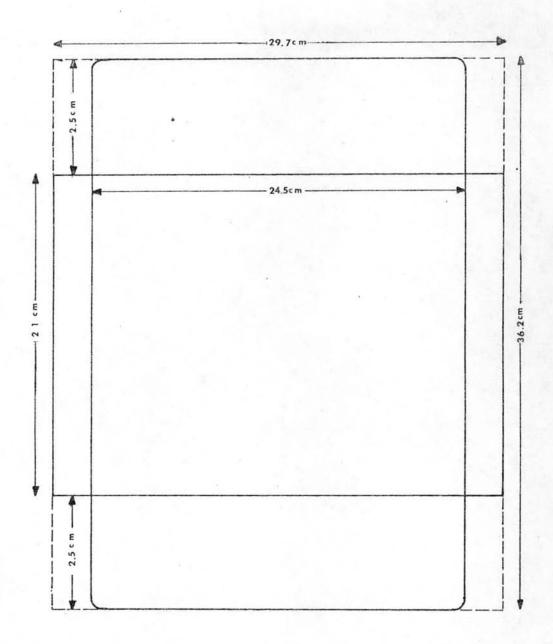

# APPENDIX C PRINTED CIRCUIT LAYOUTS

01234 56789 !

DISPLAY BOARD

SEGMENT

IDENTIFICATION

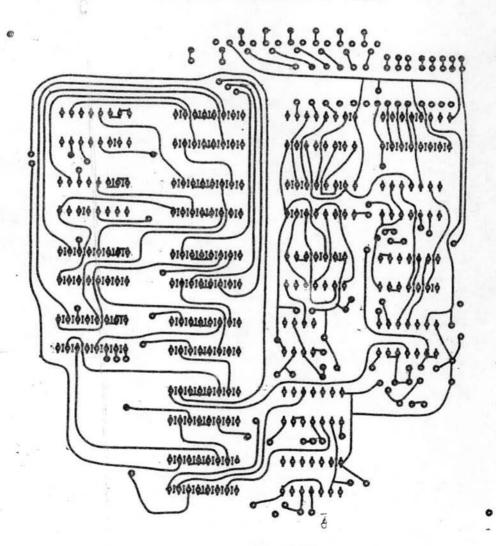

COUNTER BOARD SIDE. A

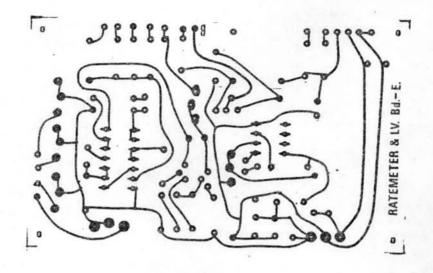

RATEMETER & LOW VOLTAGE BOARD

COUNTER BOARD SIDE B

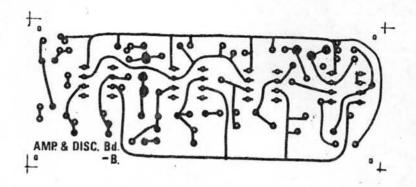

AMPLIFIER & DISCRIMINATOR BOARD

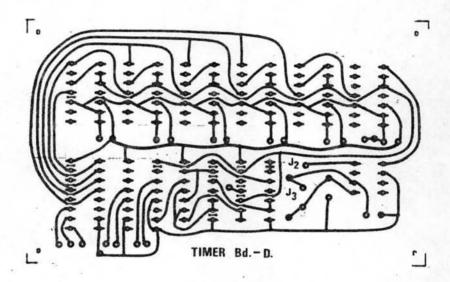

TIMER BOARD

HIGH VOLTAGE BOARD

FRONT PANEL LAYOUT

REAR PANEL LAYOUT

CHASSIS LAYOUT

#### BIOGRAPHY

Mr. Suvit Punnachaiya was born on August 29, 1954 in Chonburi,

Thailand. He received a Bachelor of Science in Technological Education,

major in Electrical Technology - Communication from the Institute of

Technology and Vocational Education in 1977. In the same year he

worked at the Department of Nuclear Technology, Faculty of Engineering,

Chulalongkorn University and continued his study towards the degree of

Master of Engineering in Nuclear Technology at the same place in 1980.

He is now working as teaching staff in the Department of Nuclear

Technology, Faculty of Engineering, Chulalongkorn University.