นายอลงกต บุรุษอาชาไนย

สายท่อการคำนวณ การทำค่าคาดหมายให้ได้มากที่สุด สำหรับทำการเพิ่มผสม

สาขาวิชาวิศวกรรมคอมพิวเตอร์ ภาควิชาวิศวกรรมคอมพิวเตอร์ คณะวิศวกรรมศาสตร์ จุฬาลงกรณ์มหาวิทยาลัย ปีการศึกษา 2555 ลิขสิทธิ์ของจุฬาลงกรณ์มหาวิทยาลัย บทคัดย่อและแฟ้มข้อมูลฉบับเต็มของวิทยานิพนธ์ตั้งแต่ปีการศึกษา 2554 ที่ให้บริการในคลังปัญญาจุฬาฯ (CUIR) เป็นแฟ้มข้อมูลของนิสิตเจ้าของวิทยานิพนธ์ที่ส่งผ่านทางบัณฑิตวิทยาลัย

วิทยานิพนธ์นี้เป็นส่วนหนึ่งของการศึกษาตามหลักสูตรปริญญาวิศวกรรมศาสตรดุษฎีบัณฑิต

The abstract and full text of theses from the academic year 2011 in Chulalongkorn University Intellectual Repository (CUIR)

are the thesis authors' files submitted through the Graduate School.

# A CALCULATION PIPELINE OF EXPECTATION MAXIMIZATION FOR ADMIXTURE APPLICATION

Mr. Alongkot Burutarchanai

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy of Engineering in Computer Engineering Department of Computer Engineering Faculty of Engineering Chulalongkorn University Academic Year 2012 Copyright of Chulalongkorn University

| Thesis Title   | A CALCULATION PIPELINE OF EXPECTATION    |

|----------------|------------------------------------------|

|                | MAXIMIZATION FOR ADMIXTURE APPLICATION   |

| Ву             | Mr.Alongkot Burutarchanai                |

| Field of Study | Computer Engineering                     |

| Thesis Advisor | Professor Prabhas Chongstitvatana, Ph.D. |

Accepted by Faculty of Engineering, Chulalongkorn University in Partial Fulfillment of the Requirements for the Doctoral Degree

..... Dean of the Faculty of Engineering (Associate Professor Boonsom Lerdhirunwong, Dr.Ing.)

THESIS COMMITTEE

..... Chairman

(Professor Boonserm Kijsirikul, Ph.D.)

...... Thesis Advisor

(Professor Prabhas Chongstitvatana, Ph.D.)

..... Examiner

(Assistant Professor Setha Pan-ngum, Ph.D.)

..... Examiner

(Assistant Professor Sukree Sinthupinyo, Ph.D.)

..... Examiner

(Sissades Tongsima, Ph.D.)

อลงกต บุรุษอาซาไนย : สายท่อการคำนวณ การทำค่าคาดหมายให้ได้มากที่สุด สำหรับ ทำการเพิ่มผสม (A CALCULATION PIPELINE OF EXPECTATION MAXIMIZATION FOR ADMIXTURE APPLICATION). อาจารย์ที่ปรึกษาวิทยานิพนธ์หลัก : ศาสตราจารย์ ดร.ประภาส จงสถิตย์วัฒนา, 61 หน้า.

วิทยานิพนธ์นี้น้ำเสนอวิธีคำนวณการเพิ่มผสมซึ่งเป็นเครื่องมือในการวิเคราะห์ส่วนผสม ของพันธุกรรมต้นกำเนิดของเผ่าพันธุ์ต่างๆ โดยรูปแบบการคำนวณจะถูกเปลี่ยนมาอยู่ในรูปแบบ ฟังก์ชันควรจะเป็น ซึ่งฟังก์ชันควรจะเป็นนี้มีการประยุกต์การทำค่าคาดหมายให้ได้มากที่สุดเข้ามา ในการแก้ปัญหาฟังก์ชันควรจะเป็น การแก้ปัญหาฟังก์ชันควรจะเป็นมีการเสนอระเบียบวิธีการ ต่างๆ ที่ตั้งอยู่บนขบวนการทำซ้ำซึ่งต้องการการคำนวณจากหน่วยประมวลผลอยู่มาก อีกทั้งข้อมูล ที่ใช้ในการประมวลผลเป็นข้อมูลพันธุกรรมของสิ่งมีชีวิตซึ่งมักจะมีขนาดใหญ่เพื่อเพิ่มความ แม่นยำของการคำนวณ จึงทำให้การคำนวณนี้ใช้เวลาในการคำนวณนาน งานวิจัยนี้จึงได้มีการนำเสนอเครื่องมือที่ใช้การคำนวณการเพิ่มผสมรูปแบบใหม่ ด้วยเกตอะเรย์ ชนิดโปรแกรมได้ เนื่องจากเกตอะเรย์ชนิดโปรแกรมได้มีประสิทธิภาพการคำนวณข้อมูลแบบจุด ทศนิยม และ สามารถสังเคราะห์ตัวดำเนินการจุดทศนิยมได้มากกว่า หน่วยประมวลผลทั่วไป อีก ทั้งรูปแบบการคำนวณของการทำค่าคาดหมายให้ได้มากที่สุดเหมาะสมกับเกตอะเรย์ชนิด ์ โปรแกรม งานวิจัยนี้ประยุกต์สถาปัตยกรรมซีสโตลิก (Systolic architecture) ร่วมกับการออกแบบ ้วงจรคำนวณ โดยสถาปัตยกรรมนี้ส่งข้อมูลขาเข้าในรูปแบบสายท่อ เนื่องจากสถาปัตยกรรมซีส โตลิกผนวกกับเกตอะเรย์ชนิดโปรแกรมได้จึงสามารถออกแบบวงจรที่ลดปัญหาจากการสื่อสาร ระหว่างหน่วยประมวลผลกับหน่วยความจำที่เป็นหนึ่งในสาเหตุหลักของตัวหน่วงการคำนวณ เกตอะเรย์ชนิดโปรแกรมได้ และยังสามารถลดปัญหาการสื่อสารของหน่วยประมวลผลทำให้ สามารถเพิ่มประสิทธิภาพการคำนวณได้ถึง 4.5 เท่า ที่ความถี่สัญญาณนาฬิกา 25 เมกะเฮิรตซ์ เมื่อเทียบกับหน่วยประมวลผลสี่แกนที่ความถี่สัญญาณนาฬิกา 2.4 กิกะเฮิรตซ์

| ภาควิชา    | วิศวกรรมคอมพิวเตอร์   | ลายมือชื่อนิสิต                        |

|------------|-----------------------|----------------------------------------|

| สาขาวิชา   | .วิศวกรรมคอมพิวเตอร์. | ุลายมือชื่อ อ.ที่ปรึกษาวิทยานิพนธ์หลัก |

| ปีการศึกษา | 2555                  |                                        |

# # # 5071828421: MAJOR COMPUTER ENGINEERING KEYWORDS: ADMIXTURE / EXPECTATION MAXIMIZATION / LIKELIHOOD / FPGA ALONGKOT BURUTARCHANAI: A CALCULATION PIPELINE OF EXPECTATION MAXIMIZATION FOR ADMIXTURE APPLICATION. ADVISOR: Prof. PRABHAS CHONGSTITVATANA, Ph.D., 61 pp.

This thesis presents a calculation method of Admixture. Admixture is a tool to stratify the genotype data to infer the mixing ratio of its ancestry groups. Likelihood calculation was proposed to represent the admixture calculation. Expectation Maximization method was proposed to solve the likelihood problem. Expectation Maximization is based on an iterative mehod that takes very long time. Moreover, the calculation time is too slow for large genetic data.

This dissertation proposed a design of FPGA for likelihood calculation. The FPGA has high floating-point operation performance and the calculation is suitable for FPGA. The number of floating point circuit that can be instantiated is more than the floating point units in a general processor. Systolic architecture was applied to the design. The systolic architectute and FPGA can directly stream the input data to the calculation unit. The streaming of input data reduces the memory overhead. The memory overhead is a main bottleneck of the calculation. Furthermore, the design of FPGA connection can reduce the communication cost of each calculation unit. The FPGA operated at 25 MHz gains speed up 4.5x when compared to a single core processor operated at 2.4GHz.

| Department     | Computer Engineering | Student's Signature |

|----------------|----------------------|---------------------|

| Field of Study | Computer Engineering | Advisor's Signature |

| Academic Year  | .2012                |                     |

# ACKNOWLEDGEMENT

It would not have been possible to write this doctoral thesis without the help and support of kind people around me, to only some of whom it is possible to give particular mention here. I would like to thank every of my committee Prof. Boonserm Kijsirikul, Ph.D, Asst. Prof. Setha Pan-ngum, Ph.D, Asst. Prof. Sukree Sinthupinyo, Ph.D for every of their helps and their hospitality to improve this dissertation. This thesis would not have been possible without the help, support and patience of my supervisor, Prof. Prabhas Chonstitvatana. Ph.D.. He is a very good advisor, very good friend. Furthermore, he also inspires and clearifies many of my though. I am extremely grateful with him.

I would like to Very thank ISL ISL2 and ELITE members to fulfill my studying life here. They gave and shared a lot of knowledge, idea and social.

Thank to P'Nun, Anunchai Assawamakin, Ph.D. and BIOTEC's member to share the research topic, biological knowledge. The members are also my advisoron biology. Many of my circuits were inspired by the team.

Finally, I would like to thank my family and my dearest friend Miss Patcharaporn Laohatweechoke for their personal support. They alway give me very warmth and love, although they do not understand what I did.

# CONTENTS

| page                                   |

|----------------------------------------|

| HAI ABSTRACTd                          |

| ENGLISH ABSTRACTe                      |

| ACKNOWLEDGEMENTf                       |

| CONTENTSg                              |

| -<br>ABLEi                             |

| -<br>IGURESi                           |

|                                        |

| CHAPTER 1 INTRODUCTION 1               |

| 1.1 Rekated works                      |

| 1.1.1 Algorithm Development            |

| 1.1.2 Technoloty of Calculation        |

| 1.2   Problem Statement                |

| CHAPTER 2 METHODS AND BACKGROUND7      |

| 2.1 Mixture Models                     |

| 2.2 Hardy-Weinberg Law8                |

| 2.2.1 Allele and SNP8                  |

| 2.2.2 Diploid9                         |

| 2.2.3 Binomial Distribution            |

| 2.3 Likekihood Model10                 |

| CHAPTER 3 DESIGN AND IMPLEMENTATION 14 |

| 3.1 Floating Point                     |

| 3.2 Circuit Design of EM calculation16 |

| 3.2.1 Circuit Design for UpdateP17     |

| 3.2.2 Circuit Design for UpdateQ19     |

| 3.2.3 Circuit Design for UpdateAB21    |

| 3.2.4 Circuit Design Summary24         |

| 3.3 Systolic Array                     |

| Page |

|------|

|------|

| 3.3.1    | Circuit Design for Maximization Calculation26 |

|----------|-----------------------------------------------|

| 3.3.2    | 2 Circuit Design for Expectation Calculation  |

| 3.4      | Circuit Implementation                        |

| 3.4.1    | Register Unit                                 |

| 3.4.2    | 2 Calculation Unit: Wrapping Circuit          |

| 3.4.3    | 3 Control Unit                                |

| 3.4.4    | The sub-calculation unit of updatePQ37        |

| 3.4.5    | 5 The sub-calculation unit of updateAB        |

| 3.4.6    | Byte-Float Multiplication block (Mul012)      |

| CHAPTER  | R 4 SUMMARIZATION AND FUTURE WORKS40          |

| 4.1      | Dissertation Summarization                    |

| 4.2      | Design Summarization of Hardware Utilization  |

| 4.3      | Calculation result                            |

| 4.4      | Results                                       |

| 4.5      | Hardware and Software performance             |

| 4.5.1    | Single Core                                   |

| 4.5.2    | 2 Multi Core                                  |

| 4.5.3    | 53 FPGA                                       |

| 4.6      | Future works                                  |

| REFEREN  | NCE                                           |

| Biograph | y 61                                          |

# TABLES

| page                                                                                     |

|------------------------------------------------------------------------------------------|

| Table 1 The sub-calculation unit usage in each circuit and the number of the circuit for |

| overall circuit                                                                          |

| Table 2 The size of register allocation                                                  |

| Table 3 Control signal to enable the wrapping circuit                                    |

| Table 4 The hardware resource usage of floating point adder for Spartan-341              |

| Table 5 The hardware resource usage of floating point multiplier for Spartan-3           |

| Table 6 The hardware resource usage of floating point dvider for Spartan-3 42            |

| Table 7 The hardware resource usage of floating point adder for Virtex-6       42        |

| Table 8 The hardware resource usage of floating point multiplier for Virtex-6            |

| Table 9 The hardware resource usage of floating point dvider for Virtex-6                |

| Table 10 The hardware utilization of a block of Mul012 operator for Virtex-6             |

| Table 11 The resource utilization of updateQ circuit for Virtex-6                        |

| Table 12 The resource utilization for each type of updateP for Virtex-6                  |

| Table 13 The resource utilization of updateAB for Virtex-6       46                      |

| Table 14 The hardware resource utilization of Frappe calculation circuit                 |

| Table 15 The hardware usage for the calculation circuit that composes of 5 individuals   |

| 10 markers and 3 ancestral groups                                                        |

| Table 16 The hardware usages for the register circuit that composes of 5 individuals 10  |

| markers and 3 ancestral groups                                                           |

# FIGURES

| page                                                                                        |

|---------------------------------------------------------------------------------------------|

| Figure 1 Tandem repeat2                                                                     |

| Figure 2 Mixing of two groups of ancestry when the time is changed                          |

| Figure 3 Show the genetic mixing from four population in each time step                     |

| Figure 4 Show a chunk of chromosome and SNPs8                                               |

| Figure 5 Show the mixture models that composed of four difference binomial distribution     |

| models                                                                                      |

| Figure 6 Show the register allocation in FPGA circuit                                       |

| Figure 7 show 32-bit width of IEEE754 format for floating point calculation                 |

| Figure 8 the "UpdateP" circuit in column 0 19                                               |

| Figure 9 the circuit of UpdateQ                                                             |

| Figure 10 The circuit of UpdateAB: genotype is "0". The genotype of each copy is Major      |

| or Homogenous wild type. Only ancestral major allele frequency was selected                 |

| Figure 11 The circuit of UpdateAB: genotype is "1" (Heterozygous). Both Major and           |

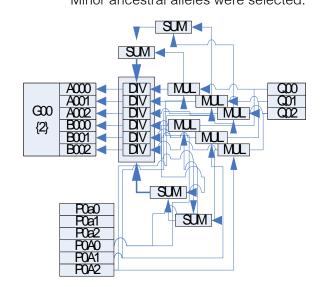

| Minor ancestral alleles were selected                                                       |

| Figure 12 The circuit of UpdateAB: genotype is "2". Only ancestral minor allele             |

| frequency was selected                                                                      |

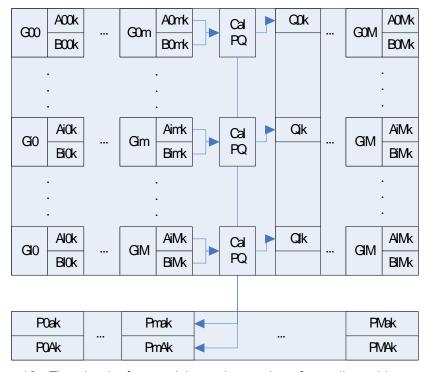

| Figure 13 show the data partitioning for feeding into each architecture of calculation unit |

|                                                                                             |

| Figure 14 show Data Processing Units (DPUs) of Systolic Architecture                        |

| Figure 15 The original circuit of the maximization part of likelihood calculation27         |

| Figure 16 The circuit after apply column-wise of systolic architecture to the maximization  |

| step                                                                                        |

| Figure 17 The circuit of updatePQ circuit of systolic architecture                          |

| Figure 18 The circuit for expectation step                                                  |

| Figure 19 The timing diagram of floating point multiplier circuit                           |

| Figure 20 The timing diagram of floating point adder circuit                                |

| Figure 21 The timing diagram of floating point divider circuit                              |

| Figure 22 The original circuit and wrapping circuit of a floating point adder               |

| Figure 23 The input part of the wrapping block                                              |

page

| Figure 24 A part of calculation in updataQ circuit                                      |

|-----------------------------------------------------------------------------------------|

| Figure 25 The wrapping circuit of adder that composes of AND gate and DFF               |

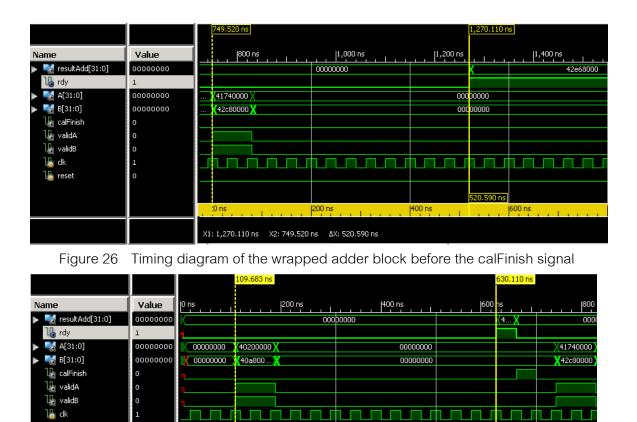

| Figure 26 Timing diagram of the wrapped adder block before the calFinish signal 36      |

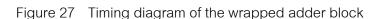

| Figure 27 Timing diagram of the wrapped adder block                                     |

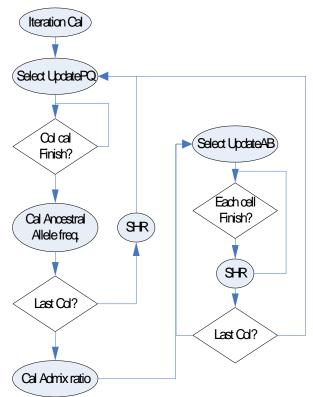

| Figure 28 The control logic in an iteration of EM                                       |

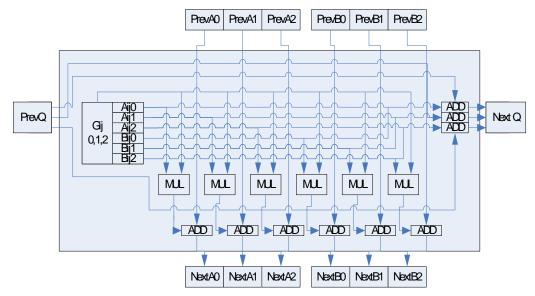

| Figure 29 The connection of sub-unit calculation for each cell in updatePQ circuit 38   |

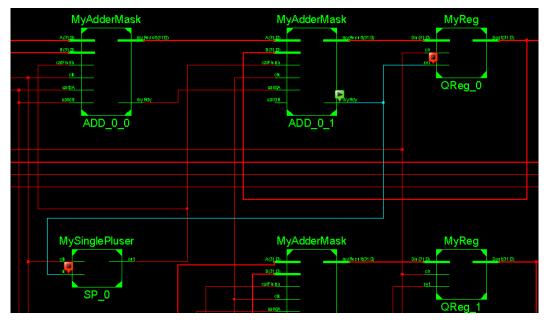

| Figure 30 The connection of calFinish within the calculation block                      |

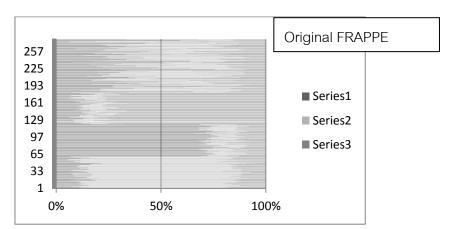

| Figure 31 The result of admix ratio from the simulation data with original FRAPPE       |

| application                                                                             |

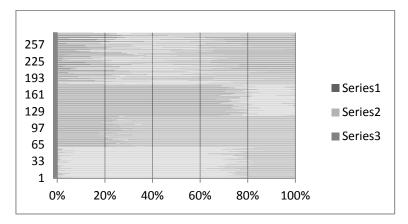

| Figure 32 The result of admix ration from the simulation data with double precision re- |

| implemented application                                                                 |

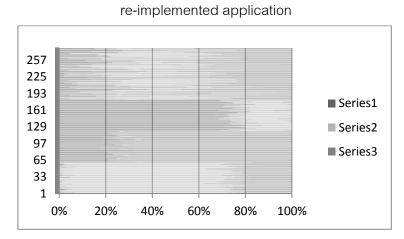

| Figure 33 The result of admix ration from the simulation data with single precision re- |

| implemented application                                                                 |

| Figure 34 the calculation of updateQ for single core processor                          |

| Figure 35 the column-wise architecture, the calculation loop of updateP for a single51  |

| Figure 36 the calculation of updateAB for a single cores processor                      |

| Figure 37 the operation of updateQ for multi-processing unit                            |

| Figure 38 the placed calculation circuits and register units of row-wise access         |

| Figure 39 the calculation block connection for column-wise access                       |

# CHAPTER 1

## INTRODUCTION

Admixture Analysis is a tool to study the stratification of population. It is useful for genetic association studies [1] such as admixture mapping [2][3][4], subspecies classification [1] or genetic barrier detection [5]. The result of this analysis is the proportion of each ancestral genetic group. The aim of the analysis is to infer the mixing ratio of each unknown ancestral group from the known current genetic population data. Tang proposed a method for an individual admixture analysis [6]. This analysis can infer the admix ratio from one ancestry groups of each individual. The calculation can be a tool to infer the Hapmap tree [7][8]. Furthermore, this analysis was applied in some epidemiology genetic such as, obesity, breast cancer, the skin pigment of women who receive genetic from Hispanic and African-American [9] or diabetes of African-American [10]. However, the data to infer the stratification should be large to gain more accuracy. The large dataset takes very long time to process. Some dataset takes several months.

Admixture analysis is an ancestry estimation tool based on a maximum likelihood relation. Expectation Maximization (EM) [11][12][13] is a method to solve the likelihood relation. There are basic mathematic operators to be used in EM: random, addition, subtraction, division and multiplication. While other methods are based on numerical methods such as Newton-Raphson, NR, [14] or Block Relaxations, BR, 0. Most of NR and BR operators are matrix operators, the matrix operators were used to compute a Jacobian or Hessian matrix from the relation.

Field Programming Gate Arrays, FPGA [21], is a choice to speed up the calculation because the operators of FPGA work in fully parallel mode and they have low power consumption. Furthermore each unit of calculation of FPGA operates independently. The different calculation can be executed at the same time. Most other parallel processors are homogeneous. Currently, most of calculation speed can be gained by using parallel paradigm such as GPGPU [22][23] or Cloud Computing from Amazon [24]. Most of the techniques are done in the software level, so they cannot control each unit of calculation directly. Every commands are passed to Operating System which in turn accesses the hardware level. This work presents a method to control each unit of calculation directly.

#### 1.1 Related works

Related works in this dissertation were separated into two parts. The first part is the development of algorithms on the likelihood calculation. The second part is the development of calculation technologies.

#### 1.1.1 Algorithm Development

Admixture analysis has been developed for a long time since 1986[3], starting from allele frequency comparison which is the first approach of this field. The work was based on prior knowledge techniques. Various types of genetics representation were applied with the comparison technique such as microsatellite or Short Tandem Repeats (STR) counting. STR is a repeat of genetic base. The length of the tandem is 2-6 bases. The number of repeats is not more than 100 repeats. The tandems are show in Figure 1

------ (AATG)(AATG)(AATG)(AATG)------ 4 repeats ------ (AATG)(AATG)------ 2 repeats

Figure 1 Tandem repeat

STR was also used in forensic work in the step of PCR. Inferring the admixture of each individual was based on the known tandem data. The tandem data should be a common sequence of the parental genome and current genome. Determining the admix ratio of each individual requires the knowledge of ancestry group marker. In 1991 Long [1] proposed the algorithm to analyze the admix ratio using F-statistic,  $F_{st}$ ,[25], and Chi-square statistic applied to candidate the markers to analyse the admixture of the SNPs data. The selected markers by Long require a genomic knowledge; the markers to be used by Long must be an ancestry informative marker (AIM). An AIM [26] requires many of biology knowledge and prior knowledge of the ancestry population genetic. The result that obtained from Long is a group level admixture ratio. The information of  $F_{st}$  represents an admix ratio in group level.  $F_{st}$  is a statistical tool to measure the correlation between groups of genetic data.  $F_{st}$  is based on a deviation of the allele

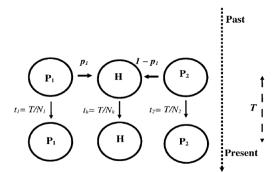

frequency represents in binomial distribution. In 2003, Carrie and et al. [26] analyzed the accuracy of the analysis of STR and SNP. The work stated that SNPs data is better than the STR data for the admixture calculation. In 2000, Pritchard [27] proposed the method of calculation by applying the Markov Chain to the admixture calculation. Pritchard et al. introduced the STRUCTURE version 1. The STRUCTURE version 1 is software to infer models from the admixture group of data. This group of genomic data was inherited from some group of ancestral group. The proposed method is a kind of statistical method that does not required ancestry genomic knowledge, such as AIM or genetic inheritance knowledge. In 2003 Falush et al. [29], proposed a STRUCTURE version 2. Multi loci of genetic data were applied with this version of STRUCTURE. The calculation was based on Linkage Disequilibrium and Allele frequency. The STRUCTURE software gains a lot of accuracy in the population level. The calculation can only be applied in the population level and it takes a lot of calculation time. Chikhi et al. proposed likelihood based calculation in 2000 [28]. Figure 2 shows the mechanic of the mixture model calculation of two groups of ancestry.

Figure 2 Mixing of two groups of ancestry when the time is changed

This method based on calculation of mixture models as Eq 1 that is based on Bayesian's network. The work proposed a speed up method for the calculation by Monte Carlo method. The work is an inference of genetic data in a population level but the genetic knowledge were applied in the calculation. The likelihood in this work is based on linear combination of each group of population. Three parameters were proposed in Eq 1, the first parameter is probability of ancestry group ( $p_i$ ), the second parameter is admix ratio ( $x_i$ ) and the last parameter is generation of mixing ( $t_i$ ). The calculation is based on current data, D to infer p and x.

Eq 1.  $L(p_1, p_2, t_1, t_2, t_h, x_1, x_2|D)$

In 2005, Tang [6] proposed a log-likelihood model for admixture calculation. The proposed method computes this model by Expectation Maximization, EM. FRAPPE is software by Tang to calculate the admixture ratio in Individual level. Tang proposed two methods in his work. The first method is EM and the second is Newton-Raphson (NR). EM was selected in his work because the implementation of NR is more difficult as the number of ancestral groups grows. Both of the approaches cannot guarantee the global maxima for non-convex relation. To solve any non-convex relationship the calculation must be re-run by changing the initial point. In 2009, Alexander et al 0 proposed a method of block relaxation for the Admixture by log-likelihood relation. ADMIXTURE was provided by Alexander. ADMIXTURE is software for admixture analysis. Quasi-Newton-Raphson (QNR) was applied to solve the likelihood relation. The calculation achieves the speed of calculation via QNR. The NR is a Quadratic time algorithm. Both of iterative methods cannot guarantee any of global convergence with non-convex problems. For NR and QNR, the starting point of calculation must be known. Most of NR guarantee a good convergence if the starting point is close to the answer.

Most of the works above are based on single-core machines and they are slow on a large dataset. Every proposed methods may get stuck at a local maximum. Using parallel programming can reduce the computation time but it is very hard to achieve good performance across variable size of dataset because there were too many choices to consider. There were two major division of work in parallel computing, first is communication and second is computation. Both of them should be balanced to gain most speed.

#### 1.1.2 Technology of Calculation

Recently, there are a lot of computing technologies such as multi-core CPU, GPU (Graphics Processing Unit), FPGA. Moore's Law states that the number of transistors on a device doubles every two years because more transistors can be fabricated in a die. An improvement of clock frequency is another factor of performance gain. This dissertation proposed a calculation of Admixture by FPGA. Many works showed the performance of FPGA is better than the performance of GPU and Multi Cores, especially the floating point calculation. In [15], Stephanie and Jason proposed acceleration of phylogenetic tree calculation by FPGA. This work achieves 10x speed up relative to the calculation by software only. The computing tasks were divided into two tasks, the first task is the performance-critical task and the second

4

task is non-performance-critical. The first task was assigned to a FPGA and the second task was assigned to a general CPU. The non-performance-critical is data manipulation task such as data swapping, sampling or moving data. While the performance-critical is the task that requires fixed point and floating point calculation. Finding a phylogenetic tree is an application of this work. Bayes' Net was applied for the calculation. Markov Chain Monte Carlo (MCMC) was applied to speed up the calculation of the Bayes' Net. The problem is formulated as a statespace-search. MCMC guesses a reasonable direction of the search to the state-space-tree. The direction at each node was obtained from the calculation of every nodes under that node. FPGA was applied to calculation the reasonable direction of the current node then trace to the selected direction until reach the leaves node. Virtex-2 Pro 100 FPGA was used as the acceleration device. The device operates at 165 MHz, but it can be operated at 310 MHz using Virtex-6 SX 475 FPGA technology. Several of FPGA applications were applied with streaming data and signal processing such as [16]. Peter and Desmond proposed a technique of decoder calculation. The FPGA was used to process the Alamouti decoder [16] to increase system capacity and performance throughput of multiple input and output antennas (MIMO). There was a report to show the floating point operation performance of FPGA vs. CPUs in [17]. This work showed the trends of both single and double precision floating point performance of the FPGA above the CPUs. The benchmark in this work is LINPACK, the linear algebra of floating point calculation and matrix operations. In 2010, Christian et al did an application to compare the overall performance on FPGA Multi-Core CPUs and GPU [19]. The application is a real-time network intrusion detection system. ReMIND [20] is a detection tool in this work. The main concept of this work is matching subsequence in packet contents by efficient sorting. This work proposed and implemented a merge-sort, bitonic-sort and insertion-sort for all testing platforms. FPGA in this work is Virtex-5 with 0.55 GHz clock frequency, two Quad-core Xeon 5472 3GHz with OpenMP C/C++ and Nvidia Quadro FX 5600 1.35GHz of clock with CUDA. Multi-core CPUs gain highest performance in this work at 2Gbits per second, while the second rank is FPGA with 2Gbit per second of operation time but 1Gbit per second of data transferring and the bottom rank is GPU at 8Mbit per second. Moreover, the data format of the FPGA has more freedom than simple data format of general processors units [18]. Chunk of memory may be implemented for each calculation unit in the high density FPGA that can get rid of the bottleneck between processing unit and memory unit especially using multi processing units on a single

data. In a general purpose processing unit, there is only a single memory connection through memory. This architecture aimed to save space on chip and routing space on a circuit, but it increases the latency of memory accessing. The IEEE 754 floating point [45] was applied in this dissertation, because it is broadly used in all the current floating point calculation units such as AMD or Intel FPU [17]. EM NR and BR calculation are based on iteration method. The result is dependent on a good initial point and the number of iteration. The convergence of any method may requires more than ten thousand iterations of calculation. The huge number of iteration can cause a lack of precision from the cumulative error of fixed point representation.

# 1.2 Problem statement

Although Moore's law claimed the hardware resource scaled at 2x every year. But the demand of calculation is increased much more than that. Most of calculation devices have weakness because of lack of hardware, such as RAM is not enough or loss of precision in a low bit of fixed point number format. This dissertation proposed a systematic improvement of EM on FPGA that is scalable by the number of ancestor group. In admixture calculation, the number of individual and the number of marker were fixed but the number of ancestral group is unknown. This is a problem for both software application and hardware application to prepare a space of RAM in software application or the number of Register in hardware application for allocation the huge size of variables. The advantage of FPGA is a freedom of design such as scattering of memory into a small chunk of memory per calculation unit. Although the clock frequency of an FPGA is not competitive with CPU from Intel or AMD or GPU, but the FPGA can create a large amount of calculation unit to simultaneously operate. Scattering of memory can reduce the bottleneck of general processing unit and memory unit. It integrates the memory unit into the calculation unit, same as register of Intel 808x or local memory of GPGPU. The design these Scattering units are scalable by number of ancestry groups.

# CHAPTER 2

## METHODS AND BACKGROUND

#### 2.1 Mixture models

Mixture model [30] is a probabilistic model derived from the existing and known data (Figure 3). There were four genetic models from four groups of population in Figure 3. Each model can be represented by  $P_1$ ,  $H_1$  represents a hybrid from parental groups. Ci represents the Child. The number in each circle denotes the number of population in each group of population. From Figure 3 there were 100 individuals in population 1, 500 individuals in population 2, 400 individuals in population 3 and 1000 individuals in population 4. It is not the case that all of the population from each group transfer their genetic to their child, for example  $H_1$  received 50 individual from  $P_1$  and 200 individuals from  $P_2$ . This relation can be written as  $H_1 = 0.2P_1 + 0.8P_2$ . While  $H_2$  received only genetic from  $P_2$  so  $H_2 = 1.0^*P_2$ . Hardy-Weinberg law [31][32] can be applied to express this fact.

Figure 3 The genetic mixing from four population in each time step

C2 population in Figure 3 may directly inherited from only one group of ancestry as  $C_2 = 1xP_4$  although the population is not the same as their ancestry, while population of C1 may mixed well with every groups of ancestry, the roots of the tree are P1, P2, P3 and P4 that formed C1.

# 2.2 Hardy-Weinberg Law [31][32]

The law explains the ratio of genetic from generation to generation. It is preserved and will not change over time. The allele frequency was persevered over time. The law can be used to explain the effect of Mendel's Pea Experiment [33].

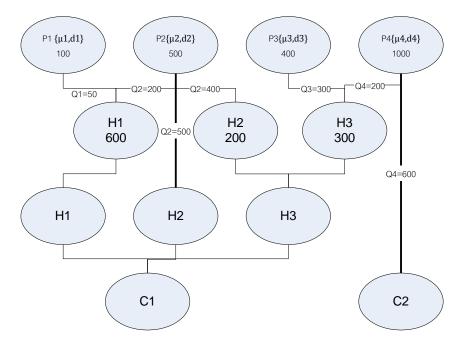

## 2.2.1 Allele and SNP [34][35]

Allele is a set of possible genetic base in a locus of diploid. There were "Major Allele" represents the majority of allele in a locus and another set called "Minor Allele". The Major and Minor Allele may not express in a phenotype such as phenotype of blood group representation the blood type "A" may come from genotype "AO" or genotype "AA". Homozygosity wild type is the genotype that composed of two major alleles. The genotype composed of two different alleles was called Heterozygosity. Its variant is a genotype that composed of two minor-alleles. To determine whether the gene is dominance or recessive depended on an expression of the genotype. SNP was used to represent the possibility of chromosome in a locus. There were various way to determine the value of SNPs. This dissertation uses 0, 1 and 2 to represent the Homozygosity wild type, Heterozygosity and Homozygosity variant respectively.

Figure 4 Show a chunk of chromosome and SNPs.

The two upper traits in Figure 4 were called genetic copy or "copy". For example, in blood type the first copy may represent blood type "A" and the lower trait also represent the blood type "A" then this genetic has genotype "AA", the dominance "A".

#### 2.2.2 Diploid [36]

Cells have two homologous copies of each chromosome such as a chromosome of mammal. Bacterial has only one copy of chromosome, called Haploid. In the mating of diploid a child will receive two copies of chromosome one from the mother and one from the father. Nearly all mammals are diploid organisms although all individuals have some small fraction of cells that display polyploidy.

#### 2.2.3 Binomial Distribution [36]

Genetic data in SNPs format was used in this dissertation. Any loci of SNPs data composed of only two possible alleles such as either A or T. If the amount of A is more than T then A is a major allele while another is minor allele. The number of individual is N. The composition in a loci can be either AA or AT or TA or TT. AA was called Homozygosity wild type. AT or TA obtained the same genotype were called Heterozygosity wild type and TT was called Homozygosity variant. Binomial relationship can be applied with SNPs data relation in a locus as Eq 2

Eq 2.

$$N^2 = (A+T)^2 = AA + AT + TA + TT = A^2 + 2AT + T^2$$

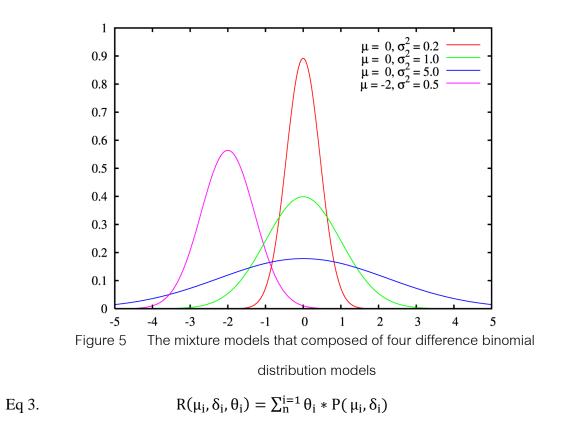

From Allele and Diploid and Hardy-Weinberg Law, a locus of SNPs data can be represented by binomial distribution model [37] as P<sub>i</sub>. There were two dependent parameters: means,  $\mu_i$  and variance, $\delta_i$  of a binomial distribution model in a locus. The mixed model may have different ratio from each ancestral group.  $\theta_i$  represents the ratio of each ancestral model. Figure 5 shows the result of mixing of four binomial models. In general, the result of mixing model can be written as the relation in Eq 3.

Mixing model was applied in STRUCTURE [29]. It is based on Markov Chain to represent the mixed model that is to find the  $\theta_i$ . This approach yields low accuracy [30]. It also does not consider the nature of genetic inheritance. Inheritance of genetic is not locus independence. Each parental genome is divided into chromosome segments, similar to a chunk of genome, and transfers to child.

## 2.3 Likelihood Model

Likelihood calculation [38] is an inverse calculation of mixture calculation. In mixture calculation, the goal is to infer the child from the known ancestry genetic distribution. For Admixture, given a mixed data, the goal is to infer the ratio of that mixing. The SNPs data do not provide any of ancestry genetic model representation and each model mixing ratio. Likelihood calculation is an inferring method to infer each unknown model representation and each unknown model ratio from the current data. The likelihood relation was proposed by Hanis in 1986 [10]. Hanis computed partial maximum likelihood with the likelihood relation. Tang applied EM with the likelihood relation. EM is a statistic based tool that was proposed by Dempster [11]. EM algorithm is a popular tool to solve the problem involving incomplete data and latent variables. EM [11] can be written as Eq 4, for likelihood model in each loci. D is a current

genetic data.  $\mu_i$ ,  $\theta_i$  are latent variables.  $\mu_i$  is an allele frequency in each ancestral group *i*.  $\theta_i$  is each ancestral group proportion.  $\delta_i$  in Eq 3 can be ignored because in the loci of SNPs the Hardy-Weinberg Equilibrium is maintained, so the likelihood relation can be represented as Eq 4.

Eq 4.

$$L(D, \mu_i, \theta_i) = \sum_{n=1}^{i=1} \theta_i * P(\mu_i)$$

EM algorithm is an iterative procedure to compute the Maximum Likelihood based on log likelihood, so the whole dataset can be written as Eq 5 after applying the log-likelihood relation.

Eq 5.

$$L(D, \mu, \theta) = \sum_{l=1}^{i=1} \sum_{M=1}^{m=1} \log \sum_{K=1}^{k=1} \theta_{ik} * \mu_{ki}$$

Dataset in this dissertation is a Single Nucleotide Polymorphisms, SNPs. SNPs is a composite of human genome data that composed of Major allele and Minor allele in each locus. There were two threads in each SNP, each thread is called copy. This means that the part of that genetic was a copy of the parent. The likelihood for mixing of genetic model in a binomial distribution is as Eq 6

Eq 6.

$$L(P,Q) = \sum_{I} \sum_{M} \{q_{ik} * p_{km}^2 + 2 * q_{ik} * p_{km}(1-p_{km}) + q_{ik} * ((1-p_{km})^2)\}$$

Eq 7 is the log-likelihood of Eq 6 and after applying the SNP value in each marker "m" of each individual "i".

Eq 7.

$$L(P,Q) = \sum_{I} \sum_{M} \{g_{im} \log \sum_{K} q_{ik} * p_{km} + (2 - g_{im}) \log \sum_{K} q_{ik} * (1 - p_{km}) \}$$

The SNPs data, G, consists of I individuals M markers,  $g_{ij}$ . Each marker of each loci has genotype either 0, 1 or 2 representing the homozygous wide type heterozygous wide type and homozygous variant type, respectively. A 0 means the first copy is "A" and the second copy is "A", A 1 means the first copy is "A" while the second copy is "a" and 2 means both the first and second copy are "a". The relationship has the term  $g_{im}log \sum_{K} q_{ik} * p_{km}$  represents the effect of only major allele. The term  $(2 - g_{im})log \sum_{K} q_{ik} * (1 - p_{km})$  represents the effect of minor

allele.  $q_{ik}$  denotes the mixing ratio from the k<sup>th</sup> ancestral group in the i<sup>th</sup> individual.  $p_{km}$  denotes the allele frequency of major allele in the m<sup>th</sup> loci of k<sup>th</sup> ancestral group, (1- $p_{km}$ ) denotes the minor allele of the m<sup>th</sup> loci of k<sup>th</sup> ancestral group.

Tang [6] proposed a method to solve the likelihood relation by Newton-Raphson (NR) as Eq 8. NR requires a differential calculation to compute the Jacobian's matrix, used in the relation. However the matrix operator in NR is difficult to scale when implemented in FPGA. Although the NR method guarantees the quadratic time of convergence [39] it does not guarantee the global solution and it is also dependent on the initial starring point.

Eq 8.

$$(P^{n+1}, Q^{n+1}) = (P^n, Q^n) - \frac{L(P^n, Q^n)}{\frac{\Delta L(P^n, Q^n)}{\Delta(P^n)}} - \frac{L(P^n, Q^n)}{\frac{\Delta L(P^n, Q^n)}{\Delta(Q^n)}}$$

Alexander proposed a block relaxation method that is based on quasi Newton Raphson. This method also does not work well with FPGA implementation. Tang proposed the calculation step of EM in three steps. They are Initialize value Step, Maximization Step and Expectation Step. The EM method must add an observable variable  $a_{im}$  for the first copy and  $b_{im}$  for the second copy at m<sup>th</sup> loci and i<sup>th</sup> individual.  $a_{im}$  and  $b_{im}$  can represent the group of ancestral value in each loci of each individual as well.

**Initial Step:** Randomly assign "1" to only one cell of k at the i<sup>th</sup> individual m<sup>th</sup> loci of a<sub>im</sub> and b<sub>im</sub>. **Maximization Step:** Maximize the value of P by Eq 9 and maximize the value of Q by Eq 10

Eq 9.

$$p_{mAk}^{n+1} = \frac{\sum_{I} g_{im} a_{imk}^{n}}{\sum_{I} g_{im} a_{imk}^{n} + \sum_{I} (2-g_{im}) b_{imk}^{n}}$$

Eq 10.

$$q_{ik}^{n+1} = \frac{1}{2M} \sum_{M} [a_{imk}^n + b_{imk}^n]$$

**Expectation step:** Re-expect the value of "A" and "B" in each marker of individual from maximized value of ancestry allele frequency and admixed ratio. The expectation step calculates the ancestry groups' ratio at m<sup>th</sup> marker from m<sup>th</sup> allele and mixing ratio of i<sup>th</sup> individual as: Eq 11 and Eq 12.

Eq 11.

$$a_{imk}^n = \frac{q_{ik}^n p_{mAk}^n}{\sum_K q_{ik}^n p_{mAj}^n}$$

Eq 12.

$$b_{imk}^n = \frac{q_{ik}^n (1 - p_{mAk}^n)}{\sum_K q_{ik}^n (1 - p_{mAj}^n)}$$

The operators in EM are simple mathematics operators. The calculations needs a high precision that FPGA support through the floating point calculation block. Convergent criterion is calculated by Eq 13

# Eq 13. $``L(P^{n+1},Q^{n+1})-L(P^n,Q^n) < e"$

"e" is stopping criteria. The iteration stops when the current likelihood value is not different from the previous likelihood value.

# CHAPTER 3

# DESIGN AND IMPLEMENTATION

This dissertation presents a method to speed up the calculation by Field Programmable Gate Arrays (FPGA) [21]. Fully parallel operators are a prefer choice of this dissertation. To achieve the performance of fully parallel calculation unit it is necessary to unroll the loop of calculation and then assign each task to each calculation unit. The limit of hardware resource causes an insufficient number of calculation units. This dissertation applies the systolic array computing to achieve scalability of the calculation. A systolic array [40] was applied to overcome a limitation of hardware resource. A systolic array is an arrangement of processors in an array where data flows synchronously across the array. The systolic array also has a specialized form of parallel computing. Each cell of arrays is an independent computing unit that computes data and stores data independently. Finally each cell shares information to the cell beside itself in the specified direction. This dissertation applied an IP-core floating point operators from the library of Xilinx [43][44] that are based on the IEEE754 standard [45] to gain more precision than fixed point calculation. A USB circuit is used as a communication channel between FPGA and PC. The synthesis and implementation tools are Xilinx ISE Design Suit v13.2 [46] with Verilog compiling language. Verilog is used to synthesis a calculation circuit and java language is used to generate a Verilog coding of the circuits from a design script.

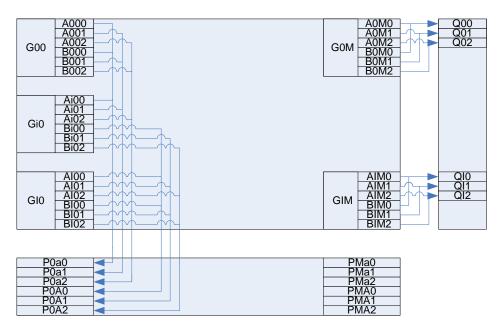

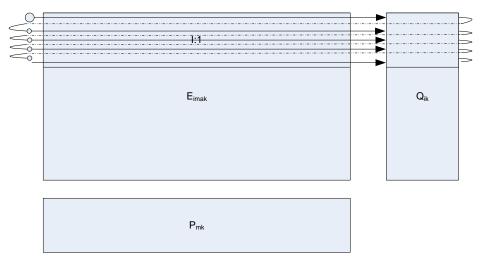

The method of a calculation starts from loading SNPs data from host CPU to FGPA. This step allocates only 2-bit per allele copy. All possible SNPs in this dissertation are {0, 1, 2}. For unknown data, it was biased to be 0. The number 0, 1 and 2 represent Homogeneous wild type, Heterogeneous and Homogeneous variant respectively. The register size of I×M×K 32-bits were allocated for "A<sub>imk</sub>" and "B<sub>imk</sub>". The P-value, Q-value and AB-value are represented by floating point single precision IEEE754 format. The Q-value allocates I×K×32-bit amount of FPGA register. The P-value allocates amount of M×K×32-bit and the AB-value allocates 2×I×M×K×32-bit of FPGA's register as shown in Figure 6. The array of registers is provided to speed up the calculation by hardware calculation as described below.

Figure 6 The register allocation in FPGA circuit

The units of registers in the calculation of the equations, in previous chapter, were represented in this Figure. There were several types of register representation in this dissertation. Floating point format was applied with register units of Aimk Bimk Qik and Pmlk while unsigned short format was applied with register unit of Gim. The vertical arrow in Figure 6 represents dependencies of Gim Aimk and Bimk on Pmlk as the Eq 9 and the horizontal arrow represent the dependencies of Aimk and Bimk on Qik as the Eq 10 as in Maximization step. The maximization step is to read the value of Pmlk and Qik and calculate as the Eq 11 and Eq 12 to update the value of Aimk and Bimk.

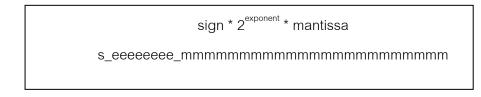

#### 3.1 Floating-Point

There are many number representations, such as the fixed point number system using 1's complement arithmetic or 2's complement arithmetic. This dissertation applied the IEEE754 floating point number format for the calculation to avoid the precision loss from the cumulative operations. Figure 7 shows the composition of IEEE754 format.

The number format is composed of three parts. The first part is a sign bit, 1-bit wide, 0 for positive and 1 for negative. The second part is an exponent, 8-bit wide in binary number and the last part is a mantissa, 23-bit wide. To transform any decimal number to the IEEE754 floating point number, it starts from a conversion to binary number then transforms to exponential form and fills in the "m" part. The exponent is transformed into a binary number and then fill to the "e" part.

A library of Floating point operation is provided by Xilinx. The operators in this dissertation are add, sub, multiply and divide. The circuits of calculation are proposed in Section 3.2.1 for updateP circuit and Section 3.2.2 for updateQ circuit and Section 3.2.3 for updateAB circuit.

#### 3.2 Circuit Design of EM calculation

The calculation of likelihood as proposed in Chapter 2 was implemented as circuits of FPGA. This dissertation proposed a method of fully parallel of processing unit. The main idea is to perform loop unrolling and scattering of memory to each calculation unit. The EM method of calculation to solve the likelihood relation as proposed in Chapter 2 was chosen. There were three steps of calculation. The first step of EM is randomized the initial point of solutions. This step is starting from randomly assigns the group of ancestral to each copy in any individual (called as initial step). The constraints of these values are  $\sum_{K} A_{imk} = 1$  to determine the probability of the major allele of the m<sup>th</sup> marker of i<sup>th</sup> individual and  $\sum_{K} B_{imk} = 1$  to determine the probability of the minor allele of the m<sup>th</sup> marker of i<sup>th</sup> individual. The second step is Maximization step as Eq 9 (updateP) and Eq 10 (updateQ). The calculation direction of Eq 9 can be simultaneously operated with Eq 10. The operation of Eq 9 is row dependent of data because the operation is based on a summation over vertical data from the first individual through the last individual of a locus. The individual admix ratio in Eq 10 is data dependent from the summation over row of each individual. The last step is Expectation step. This step redetermine the probability of ancestral group for each individual copy. The re-determining is similar to a calculation of mixture model. The step of Maximization must be completed before starting an Expectation step. The convergence of the calculation is determined by Eq 13. Each of calculation of the three steps can be implemented as follows.

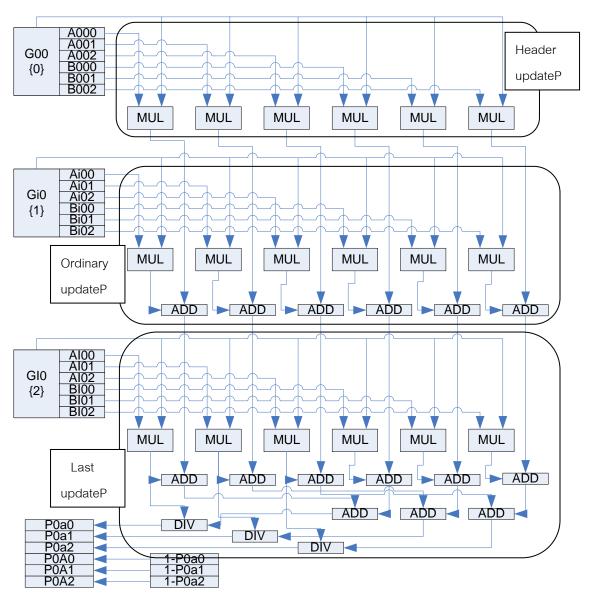

#### 3.2.1 Circuit Design for UpdateP

This circuit is used to calculate a value of ancestral allele frequency in each loci,  $P_{mAk}/P_{mBk}$  as Eq 9. It is a part of calculation to maximize the ancestry allele frequency. The calculation of each column does multiply all k variables of  $A_{im}$  by  $G_{im}$  and accumulate through the last I<sup>th</sup>. Then divide each k<sup>th</sup> variable of  $A_{im}$  by  $A_{im}+B_{im}$

| zero all P[m][k]                        |

|-----------------------------------------|

| for m = to size of Marker{              |

| for I = 0 to size of Individual {       |

| for k = 0 to size of Ancestral group {  |

| tmpA[k] = tmpA[k] + G[i][m] * A[i][m]   |

| tmpB[k] = tmpB[k] + (2-G[i][m])*B[i][m] |

| }                                       |

| }                                       |

| P[m][k] = tmpA[k] / (tmpA[k] + tmpB[k]) |

| }                                       |

The calculation does a summation over individuals in a locus and the result is a new ancestral allele frequency for the next iteration. The pseudo code shows the method of updateP that is implemented on a single processing unit. For multiple of processing units the calculation can be transformed to

| Pmk = | G0m*A0mk +G1mk*A1mk ++ Gimk*Aimk++ GImk*AImk                               |

|-------|----------------------------------------------------------------------------|

| (     | <br>G0m*B0mk ++ Gimk*Bimk++ GImk*BImk + G0m*B0mk ++ Gimk*Bimk++ GImk*BImk) |

There were three types of circuit in updateP. The first circuit multiplies  $G_{im}$  by  $A_{im}$  and  $B_{im}$  then sends the result to the second circuit. The second circuit multiplies the current  $G_{im}$  by  $A_{im}$  and  $B_{im}$  and adds the current result with the previous result, and then sends it to the next circuit through the last individual data. The third circuit is the same as the second type of updateP but it also adds a block of addition circuit between  $G_{im} \times A_{imk}$  and  $G_{im} \times B_{imk}$ . This is as a denominator of the divide circuit to complete the updateP calculation of each loci. The head of updateP circuit contains only 2k blocks of *mul* to multiply  $G_{im}$  by  $A_{im}$  and multiply  $G_{im}$  by  $B_{im}$ . There were 3 types of input ports. The first type is 2-bit wide for  $G_{0m}$ , the second type is 32-bit wide k ports for A0mk and the last type is 32-bit wide k ports for B0mk. The output ports are 32-bit wide 2k ports. It is shown as the top block of Figure 8. The updateP circuit contains 2k blocks of *mul* and *add* circuit to multiply  $G_{im}$  by  $A_{im}$  and multiply  $G_{im}$  by  $B_{im}$  and adds the result with the updateP

circuit. There were four types of input ports. The first type is 2-bit wide for  $G_{0m}$ . The second type is 32-bit wide k ports for  $A_{0mk}$ . The third type is 32-bit wide k ports for  $B_{0mk}$  and the last type is 32-bit wide 2k ports of the previous  $A_{imk}$  and the previous  $B_{imk}$ . The output ports are the same as the head of updateP circuit. It is shown as the middle block of Figure 8. The last updateP circuit is almost the same implementation and input/output port as an ordinary updateP circuit but the operator performs add of the ancestral major allele number with the ancestral minor allele number. The result is a norm of ancestral allele frequency. The k units of *add* block and *div* block were added to the circuit. The input ports are the same as an ordinary updateP but there are only 32-bit wide k ports of the output to the ancestry major allele frequency.

The calculation circuit is shown in Figure 8. Please note the connection of the three types of updateP circuit. The left side of the circuit is the register of each locus of individual. Aim implies major allele. Bim implies minor allele and G is the genotype value. The A<sub>imk</sub> and B<sub>imk</sub> have k possible values from k groups of ancestral. This value is selected to update the ancestral allele frequency of each ancestral group as  $P_{mAk}/P_{mBk}$ . The update depends on genetics value of the loci of each individual, G<sub>im</sub> = 0 means Major-Major (AA), G<sub>im</sub> = 1 means Major-Minor (AB) and G<sub>im</sub> = 2 means Minor-Minor (BB). From the relationship of binomial distribution and log-likelihood (Eq 9), the genetic value 0 denote the P<sub>0Ak</sub> += A<sub>imk</sub> + B<sub>imk</sub>. The genetic value 1 denotes  $P_{0Ak} += A_{imk}$ ,  $P_{0Bk} += B_{imk}$  and the genetic value 2 denotes  $P_{0Bk} += A_{imk} + B_{imk}$ . The ancestral allele frequencies were calculated only for Major Ancestral Allele Frequency to reduce the circuit size. The minor ancestral allele frequency is implied by 1- major ancestral allele frequency. It is shown at the bottom of Figure 8. Figure 8 shows the calculation circuit of the first marker for three ancestor groups.

Figure 8 the "UpdateP" circuit in column 0

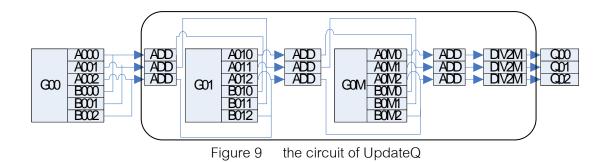

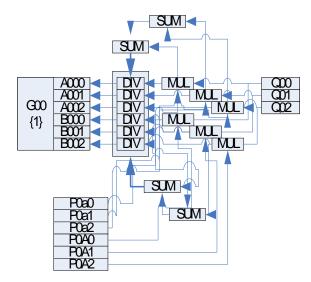

# 3.2.2 Circuit Design for UpdateQ

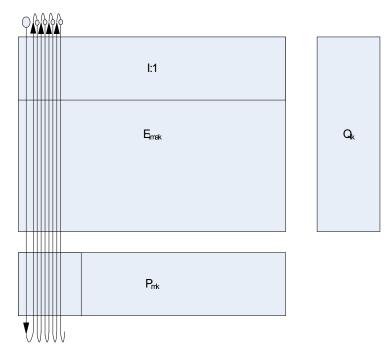

This circuit calculates the individual admix ratio ( $Q_{ik}$ ) as Eq 10. It was used in Maximization step. To update the new value of  $Q_{ik}$ , it sums every value of  $A_{imk}$  and  $B_{imk}$  that match the k<sup>th</sup> ancestral group by row (Figure 9). There is a direct connection for each k<sup>th</sup> registers in the circuit of the  $A_{imk}$  and  $B_{imk}$  because each register represents the inheritance ratio of each marker of individual. For example  $A_{123}$  represents the 3<sup>rd</sup> ancestry group probability of the 2<sup>nd</sup> marker of 1<sup>st</sup> individual. There are 32-bit wide k variables per individual to compute the mixing ratio of each ancestral group in each individual. The sum of these values in each individual is 1.0. The pseudo code of the implementation of Eq 10 is as follows. zeros all Q[I][K] for i = 0 to size of Individual{ for m = 0 to size of markers{ for k = 0 to number of ancestral groups Q[i][k] += A[i][m][k]/2M + B[i][m][k]/2M; {

The computation for a single processing unit starts from clearing the admix ratio  $(Q_{ik})$  from the previous calculation. Then cumulatively adding the value of A and B row by row through the last row. The implementation for a multiple processing unit can be implemented as follows.

| Q00 = (A000+B000+A010+B010++A0m0+B0m0++A0M0+B0M0) / 2M |

|--------------------------------------------------------|

| Q01 = (A001+B001+A011+B011++A0m1+B0m1++A0M1+B0M1) / 2M |

| Q0k = (A00k+B00k+A01k+B01k++A0mk+B0mk++A0Mk+B0Mk) / 2M |

| Qik = (Ai0k+Bi0k+Ai1k+Bi1k++Aimk+Bimk++AiMk+BiMk) / 2M |

| QIk = (Al0k+Bl0k+Al1k+Bl1k++Almk+Blmk++AlMk+BlMk) / 2M |

The implementation of individual admixture ratio is shown in Figure 9. There is only one type for input port. It is 32-bit wide and there are 2k x M x K ports for value of A and B and 32-bit wide k ports for the output. The circuit requires M x K units of computing in a row as shown in Figure 9. The sub unit calculations were applied for the entire row of genetic data per individual. Figure 9 shows a part of the calculation circuit that consists of three ancestral groups, K=3. The calculation block was connected to every register from the genotype (G) and the first and the second copies of every marker in an individual.

#### 3.2.3 Circuit Design for UpdateAB

After the calculation of the Maximization step is completed, the next calculation is the Expectation calculation. This step computes the re-expect value of the latent variables of  $A_{imk}$  and  $B_{imk}$  that imply the group of ancestry in a locus of each copy of genetic data. The values are the probability of each marker multiplied by the mixing ratio as Eq 11 for major allele and Eq 12 for minor allele. The method of calculation is to sum over ancestral groups for  $q_{ik} \times p_{mk}$  for major allele and  $q_{ik} \times (1-p_{mk})$  for minor allele. Values of  $A_{imk}$  and  $B_{imk}$  depend on the genetic data to select either major or minor ancestral allele frequency value. The pseudo code of Eq 11 and Eq 12 as follows.

| for i = 0 to size of Individual {        |  |  |  |  |  |

|------------------------------------------|--|--|--|--|--|

| for m = 0 to size of Marker {            |  |  |  |  |  |

| major = 0; minor = 0;                    |  |  |  |  |  |

| for k = 0 to size of Ancestral group {   |  |  |  |  |  |

| major = P[m][k]*Q[i][k] + major          |  |  |  |  |  |

| minor = (1-P[m][k])*Q[i][k] + minor      |  |  |  |  |  |

| }                                        |  |  |  |  |  |

| for k = 0 to size of Ancestral group {   |  |  |  |  |  |

| $A[i][m][k] = P[m][k]^*Q[i][k] / major$  |  |  |  |  |  |

| B[i][m][k] = (1-P[m][k])*Q[i][k] / minor |  |  |  |  |  |

| }                                        |  |  |  |  |  |

| }                                        |  |  |  |  |  |

| }                                        |  |  |  |  |  |

The first loop is a calculation of mixing model of the m<sup>th</sup> marker in the i<sup>th</sup> individual. The result is a denominator of each copy. This calculation was used in the second loop to represent the inheritant proportion of each copy from its ancestor. The pseudo code above shows the operation of a single processing unit. The thread of computing is started by calculating from the first marker of the first individual through the last marker of the last individual to complete the Expectation step. It is important to have the independence of data access of the calculation units to ancestral allele frequency and individual admix ratio. The design for multiple calculation units uses multiple registers to achieve this effect. Multiple registers can be accessed at the same time, assuming there were I×M units of updateAB circuits. The calculation unit of updateAB can be implemented as follows.

$$\begin{split} A[i][m][0] &= P[m][0]^*Q[i][0] / (P[m][0]^*Q[i][0] + P[m][1]^*Q[i][1] + ... + P[m][K]^*Q[i][K]) \\ B[i][m][0] &= (1-P[m][0])^*Q[i][0] / ((1-P[m][0])^*Q[i][0] + (1-P[m][1])^*Q[i][1] + ... + (1-P[m][K])^*Q[i][K]) \\ A[i][m][1] &= P[m][0]^*Q[i][1] / (P[m][0]^*Q[i][0] + P[m][1]^*Q[i][1] + ... + P[m][K]^*Q[i][K]) \\ B[i][m][1] &= (1-P[m][0])^*Q[i][1] / ((1-P[m][0])^*Q[i][0] + (1-P[m][1])^*Q[i][1] + ... + (1-P[m][K])^*Q[i][K]) \\ \\ \dots \\ A[i][m][K] &= P[m][0]^*Q[i][K] / (P[m][0]^*Q[i][0] + P[m][1]^*Q[i][1] + ... + P[m][K]^*Q[i][K]) \\ B[i][m][K] &= (1-P[m][0])^*Q[i][K] / ((1-P[m][0])^*Q[i][0] + (1-P[m][1])^*Q[i][1] + ... + (1-P[m][K])^*Q[i][K]) \\ \end{split}$$

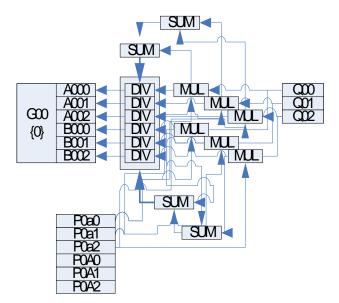

The implementation is suitable for the bottleneck-less architecture as FPGA or multiple processing units which have enough internal registers. There was 32-bit input/output bus for each unit of A and B as shown in Figure 6. The ancestral allele frequency ( $P_{mk}$ ) and individual admix ratio ( $Q_{ik}$ ) were directly accessed from each computing unit to update their own registers of  $A_{imk}$  and  $B_{imk}$ . The genotype selects  $P_{mk}$  to be calculated. The selection process of  $P_{mk}$  is shown in Figure 10, Figure 11 and Figure 12.

Figure 10 The circuit of UpdateAB: genotype is "0". The genotype of each copy is Major or Homogenous wild type. Only ancestral major allele frequency was selected.

Figure 11 The circuit of UpdateAB: genotype is "1" (Heterozygous). Both Major and

Minor ancestral alleles were selected.

Figure 12 The circuit of UpdateAB: genotype is "2". Only ancestral minor allele frequency was selected.

Figure 10 shows a calculation circuit when the genotype of the locus is "0". The circuit will select only the ancestral major allele frequency ( $P_{mk}$ ). When genotype is "1", the major and minor ancestral allele frequencies are selected. When it is "2", only ancestral minor allele frequency (1- $p_{mk}$ ) is selected to operate as Eq 11 and Eq 12 respectively. The architecture of this step is totally different from the calculation of Maximization step as 3.2.1 and 3.2.2. The genotype data is shared between multiple calculation units. For the proposed architecture here, there is no conflict in accessing data between multiple units. However, the mutual exclusion for sharing data access is a major problem for a conventional CPU.

Figure 8 - Figure 12 were proposed calculation circuits in this dissertation. Figure 6 is a circuit of register unit. The arrows in Figure 6 were operations of maximization step. The circuits in Figure 8 and Figure 9 perform concurrent update concurrently update the value of Pmlk and Qik.

#### 3.2.4 Circuit Design Summary

The architecture proposed in the previous section consumes a lot of resource as registers and a lot of floating point operation units as shown in Table 1.

| Circuit  | Number block | Number blocks of | Number blocks | Number of the block |

|----------|--------------|------------------|---------------|---------------------|

|          | of Adder     | multiplier       | of Divider    | in overall          |

| updateQ  | 2K           | -                | К             | I×M                 |

| updateP  | 2K+K         | 2К               | К             | I×M                 |

| updateAB | 2(K-1)       | 2К               | 2K            | I×M                 |

Table 1The sub-calculation unit usage in each circuit

There are a lot of floating operator blocks. The adder blocks have to instantiate I×M×(K+2K+K+2(K-1)) blocks of the overall circuit. The multiplier blocks have to be instantiated I×M×(2K+2K) blocks and I×M×(K+K+2K) blocks of the divider blocks. The huge amount of all floating point blocks overflows the resource available in FPGA devices. The calculation method of updateP and updateQ cause the abundant of carry ripple from data dependency in column and row. Even if the calculation units are fully implemented, there is still a bottleneck in speed up due to the ripple of carry. The Systolic architecture was applied to this dissertation. In general case, the multiplier circuit handles any value multiplies by genotypes value (0, 1 or 2). To reduce the size of the circuit, it is specialized to the fixed values of 0, 1 or 2. This specialization also reduces the time of floating point operation.

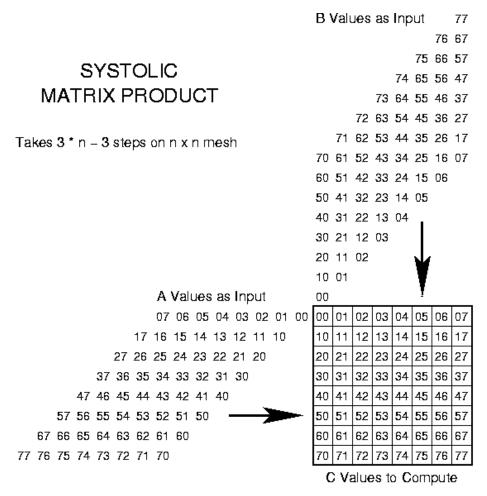

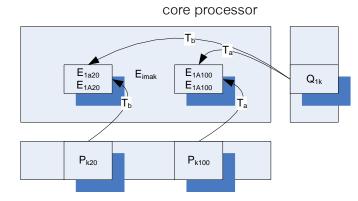

# 3.3 Systolic Array [40]

Systolic array was applied for this dissertation to reduce the number of calculation unit. Systolic array architecture is based on parallel processing and remarkable advances in VLSI technology. Many systolic algorithms have been designed for a great diversity of areas. This dissertation applies systolic architecture for hardware resource saving. The calculation step is divided into two dependent steps from Expectation Maximization algorithm. The first part is Maximization step and the second part is Expectation step. The circuit of updateP and updateQ were enabled in the Maximization step and updateAB was enabled in the Expectation step. A concern of a systolic architecture is a flow of data into the calculation units. There are several ways to flow the data into a calculation unit such feeding row-by-row as Figure 13A or feeding column-by-column as Figure 13B. The strip-wise of calculation units was called bundle-wise. Figure 13C shows the bundle-wise architecture. Figure 14 shows the flow of data by block-wise method. The data were fed through the array of Data Processing Units (DPUs) in two directions. The block-wise architecture was very popular to apply with matrix multiplication [42]. The process of matrix multiplication by systolic array is shown in Figure 14. The first step vertically feeds the B[0][0] and horizontally feeds A[0][0] to the calculation node C[0][0] to multiply and accumulate as  $C[0][0] += A[0][0] \times B[0][0]$ . The second step, the data of B[1][0] and A[0][1] are fed to process in C[0][0] and the result becomes C[0][0] += A[0][1]×B[1][0]. At this step the data of B[0][0] is fed to C[1][0] to be multiplied by A[1][0] and the result is C[1][0] += $A[1][0] \times B[0][0]$ . Other element of C is calculated similarly as  $C[0][1] = A[0][0] \times B[0][1]$ , and so on. The time complexity of matrix multiplication via systolic array is O(n) while the matrix multiplication via single thread machine takes  $O(n^3)$ , but the systolic architecture requires  $n^2$  of computation nodes.

Figure 13 data partitioning for each architecture of calculation unit

Figure 14 Data Processing Units (DPUs) of Systolic Architecture from [41]

Full placement of calculation circuit requires I×M circuits. This takes too much of resource. Placement of calculation circuits by row-wise requires M circuits. Finally placement of by column-wise requires I circuits. It is the choice in this work. Most of genetic data, the size of marker is significantly greater than the size of individual. To complete the calculation of EM, each iteration requires two steps of Expectation and Maximization. The main iterative of EM requires the first iteration or step of Maximization and another iteration is step of Expectation. Therefore, column-wise I circuits are the minimum resource required to implement this computation.

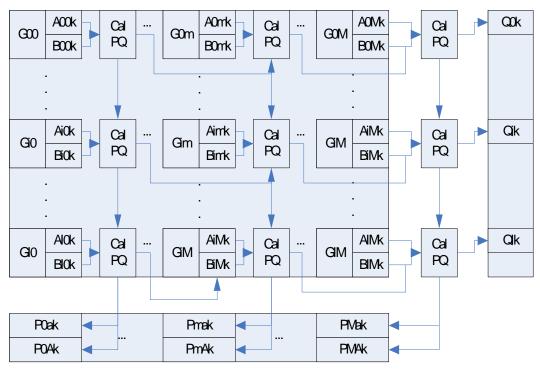

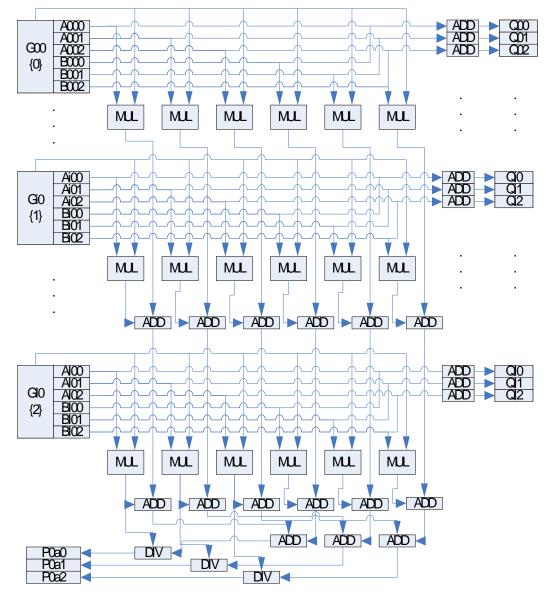

## 3.3.1 Circuit Design for Maximization Calculation

The original calculation of maximization step of EM was shown in Figure 15. There were I×M blocks of calculation circuits to process I×M array of genetic data. Figure 16 shows the

circuit after applying systolic architecture by column-wise for maximization step of EM calculation.

Figure 15 the original circuit of the maximization part of likelihood calculation

Common sub-calculation units are the most important part of the systolic architecture. The common sub-calculation units were described in Section 3.2. The implementation merges the sub-calculation units of updateP and updateQ for simultaneous calculation of maximization and update in the step of expectation. All of the implemented circuits are based on a columnwise architecture as shown in Figure 16.

Figure 16 The circuit after applying column-wise of systolic architecture to the maximization step.

Figure 16 shows the merged circuit of updateP and updateQ into CalPQ that was placed in M circuits. The horizontal operation of CaIPQ circuit performs the summation of Q[i][k] = A[i][m][k]+B[i][m][k] from the first of marker through the last of marker and divides by 2M. This operation is similar to updateQ. The horizontal operation of this circuit of each column takes O(1). It takes around 6 clocks of floating point adder. The vertical operation of the CaIPQ circuit performs the summation of the first individual through the last individual of each marker. This operation takes O(I). The circuits for ancestral allele frequency calculation were adapted for more general use than the circuit updateP. In the full placement architecture, there were three types of updateP circuit. They are differing on the value of genotype. For reusability, all of three circuits must be implemented in each CalPQ circuit, because the genetic value may be changed due to each genotype of each locus. The multiplexer of each updateP circuit was changed to multiplier block as Eq 9. The vertical operation takes O(I) from a ripple carry of each sub-calculation unit because the result of A[i][m][k]×g[i][j] and B[i][m][k]×g[i][j] has been prepared in each CaIPQ circuits as Figure 17. The time complexity of Maximization step is O(I×M), that is not significantly slower than the full placement circuit of CaIPQ or the placement by row-wise. Registers allocation of the column-wise architecture still be the same as the full placement architecture.

The flow of calculation in Maximization step started from the first locus of genetic data. The data will be shifted to the next right column when the ancestry allele frequencies of every group were updated. The circuits of CalPQ were shifted to the second locus and so on through the M<sup>th</sup> locus.

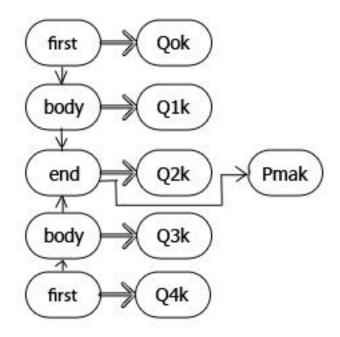

Figure 17 The circuit of CaIPQ circuit of systolic architecture.

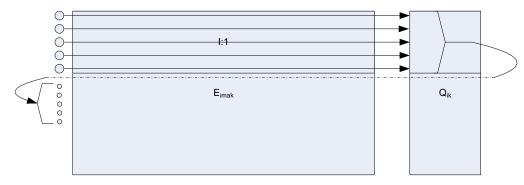

### 3.3.2 Circuit Design for Expectation Calculation

This calculation step starts after finishing of Maximization calculation. In this step the value of latent variables are updated after the parameters were Maximized, ancestral allele frequency and individual admix ratio have been maximized from the Maximization step. The original design of Expectation step is shown in Figure 10 - Figure 12. The different circuits were

selected depended on the genotype value. The genotype 0 selects the circuit of Figure 10, 1 selects the circuit of Figure 11 and 2 selects the circuit of Figure 12. The updateAB circuit in the previous section may save a hardware resource more than the circuit in this section but the previous circuit lacks of general use. The hardware resource is smaller and faster for multiplexer than the multiplier block. That is the reason why multiplexer was selected for the updateAB circuit. The multiplexer was changed to the operation of Eq 11 and Eq 12 for making a more general circuit of updateAB as Figure 18.

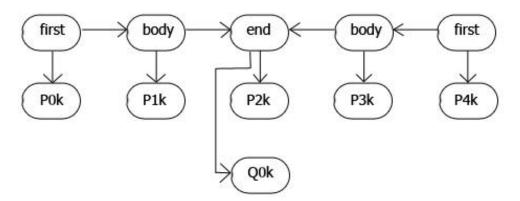

Figure 18 The circuit for expectation step.

The column-wise architecture was also applied to updateAB circuit. The time complexity of column-wise architecture is improved from O(M) to O(1). Each latent variable was updated from a separately access of ancestral allele frequency and admix ratio. There were M markers to transverse in an iteration, so the time complexity of column-wise updateAB is O(M).

The circuits of calculation are based on binary operands of floating point operators and binary operation with integer and floating point. The floating point circuit of IP-Cores from Xilinx were applied with this dissertation. This dissertation proposed a wrapping of floating point operators thus transforms them into building blocks.

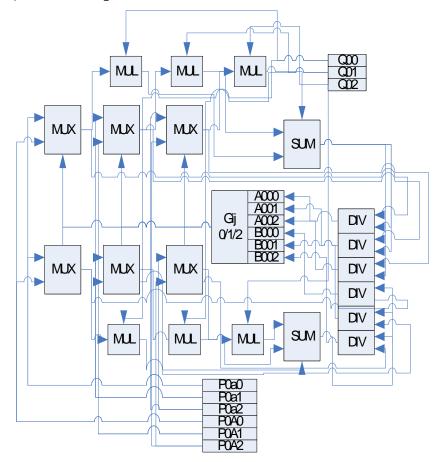

### 3.4 Circuit Implementation

This dissertation proposed an implementation of circuit via Verilog language. There are three types of circuit in this dissertation. The first circuit is Register Unit for genetic data, ancestral-allele-frequencies, admix-ratios and latent variables. The second circuit is calculation circuits for updatePQ and updateAB. The last circuit is control unit to control the flow of data and the check for stopping criterion.

### 3.4.1 Register Unit

There are four blocks of Register unit as shown in Table 2. Speed, higher accuracy and efficient hardware usage are the main aim of the design. To achieve speed up, registers are placed near the calculation units. This can reduce the bottleneck of a single data bus from data unit (RAM Cache or Register) to the calculation unit. IEEE754 floating point data format was applied with the circuit. A 32-bit data width is chosen for the implementation. The precision may not be as good as a 64-bit width but it is better than 32-bit fixed point format. Genetic data registers, only 2-bit data, are designed to fit register allocation of the circuit. The operations of both G[i][j]×A[i][j][k] and G[i][j]×B[i][j][k] were changed from 32-bit floating point operands to 32-bit floating point and 2-bit short operands.

| Genotypes        | There were I×M block of registers, each block takes two bits.  |  |  |  |

|------------------|----------------------------------------------------------------|--|--|--|

|                  | Space complexity is I×M×2 bits                                 |  |  |  |

| Admix ratios     | There were I×K block of registers, each block takes 32 bits.   |  |  |  |

|                  | Space complexity is I×K×32 bits                                |  |  |  |

| Ancestral Allele | There were M×K block of registers, each block takes 32 bits.   |  |  |  |

| frequencies      | Space complexity is M×K×32 bits                                |  |  |  |

| Latent variables | There were I×M×K blocks of register, each block takes 32 bits. |  |  |  |

|                  | Space complexity is I×M×K×32 bits                              |  |  |  |

| Table 2 | The size | of register | allocation |

|---------|----------|-------------|------------|

|         |          |             |            |

The register for Column-wise architecture were adjusted to 32×M-bit wide register.

There are I×K blocks of this register. The control unit has only the shift-left operation. These

latent variables are moved to the next 32-bit of the data and a 2-bit shift-left operation is for genotype data.

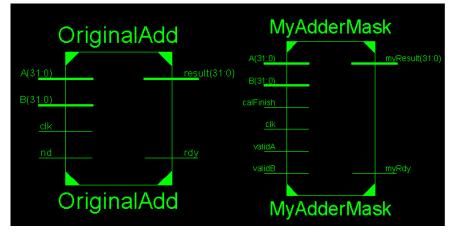

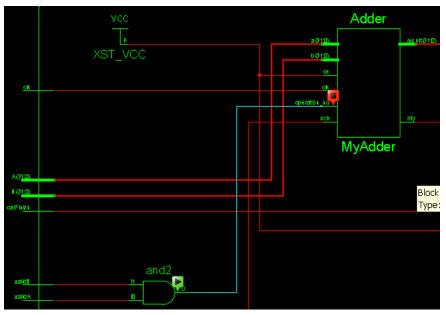

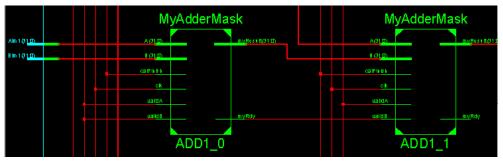

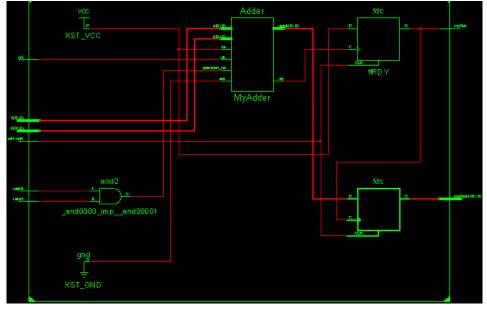

# 3.4.2 Calculation Unit: Wrapping Circuit

The calculation circuits are constructed from a basic sub-calculation block such as a floating point adder, a multiplier and a divider. Xilinx IP-cores provided the block of floating point operators used in this dissertation. This dissertation proposed a wrapping technique to envelop the floating operators of IP-cores for the proposed circuit. The wrapping technique is based on handshaking signal of Asynchronous data transfer. The operation time of each floating point operator is different. There was no register of the output signal to sustain the result. The original floating point timing diagram of Xilinx IP-cores is shown as Figure 19 -Figure 21.

|                  |          |                | 100.000 ns     |               |            |        | 428.552 ns |        |

|------------------|----------|----------------|----------------|---------------|------------|--------|------------|--------|

| Name             | Value    |                | 100 ns         | 200 ns        | 1300 ns    | 400 n  | ;<br>      | 500 ns |

| 🕨 式 result[31:0] | 41520000 | 00000000       | X              | 40000000      | X 00000000 |        | 415 0      | 000000 |

| Ug rdy           | 1        |                |                |               |            |        |            |        |

| 🕨 📑 A[31:0]      | 00000000 | 00000000       | 40200000       |               | 00000000   |        |            |        |

| 🕨 📑 B[31:0]      | 00000000 | 00000000       | (40a80000 )    |               | 00000000   |        |            |        |

| 1🔓 nd            | 0        |                |                |               |            |        |            |        |

| 1🐻 clk           | 1        |                |                |               |            |        |            |        |

| 🔚 ce             | 0        |                |                |               |            |        | 328.552 ns |        |

|                  |          |                | Ons            | 100 ns        | 200 ns     | 300 ns | 5<br>      | 400 ns |

|                  |          | X1: 428.552 ns | X2: 100.000 ns | X: 328.552 ns |            |        |            |        |

Figure 19 the timing diagram of floating point multiplier circuit

|                |          |           | 100.000 ns                                   |          |        | 587.112 ns     |          |        |  |  |

|----------------|----------|-----------|----------------------------------------------|----------|--------|----------------|----------|--------|--|--|

| Name           | Value    | 10 ns     | 200 ns                                       | 400 ns   |        | 600 ns         | 800 ns   |        |  |  |

| # Tesult[31:0] | 40f80000 | 00000000  | XX                                           | 00000000 |        | ( X X          | 00000000 |        |  |  |

| 🗓 rdy          | 1        | ,         |                                              |          |        |                |          |        |  |  |

| 🕨 📷 A[31:0]    | 00000000 | (000000)  | (40)                                         |          | 00000  | 000            |          |        |  |  |

| 🕨 📑 B[31:0]    | 00000000 | (000000)  | (40)                                         |          | 00000  | 000            |          |        |  |  |

| 1🔓 nd          | 0        |           |                                              |          |        |                |          |        |  |  |

| 🔚 clk          | 1        |           |                                              |          |        |                |          |        |  |  |

|                |          |           | Ons .                                        | 200 ns   | 400 ns | 487.112 ns     | 600 ns   | 800 ns |  |  |

|                |          | Jan Karal |                                              |          |        | <b>T</b> TTTTT |          |        |  |  |

|                |          | X1: 587.1 | X1: 587.112 ns X2: 100.000 ns ΔX: 487.112 ns |          |        |                |          |        |  |  |

Figure 20 the timing diagram of floating point adder circuit

|                  |          | 100.000 ns 1,228.269                           | ns       |

|------------------|----------|------------------------------------------------|----------|

| Name             | Value    | s  500 ns  1,000 ns                            | 1,500 ns |

| 🕨 📑 result[31:0] | 3ef3cf3d | 000 <mark>,</mark>                             | 7fc00000 |

| 堤 rdy            | 1        |                                                |          |

| u divByZero      | 0        |                                                |          |

| 1🔓 clk           | 1        | nannannannannannan                             |          |

| 🕨 📷 A[31:0]      | 00000000 |                                                | 000000   |

| 🕨 丈 B[31:0]      | 00000000 | )()() (0000000 ()) ()                          | 1000000  |

| 1🔓 nd            | 0        |                                                |          |

|                  |          | 0 ns 500 ns 1,000 ns                           | ns 11    |

|                  |          |                                                |          |

|                  |          | : 1,228.269 ns X2: 100.000 ns ΔX: 1,128.269 ns |          |

Figure 21 the timing diagram of floating point divider circuit